Key Facts

- AI Boom Strains Capacity: Explosive demand for AI accelerators has outpaced advanced packaging capacity. TSMC’s CoWoS (Chip-on-Wafer-on-Substrate) packaging is fully booked through 2025 despite aggressive expansions – capacity is doubling yearly but still can’t meet demand sourceability.com reuters.com. Nvidia’s CEO calls packaging the supply bottleneck, even after a 4× increase in capacity over two years reuters.com.

- Chiplets Go Mainstream:Chiplet architectures (multiple smaller dies in one package) now drive over $40 billion in annual revenue astutegroup.com. They power most high-end chips for AI and high-performance computing, with ~72% of AI accelerators in 2024 using advanced multi-die packaging strategicmarketresearch.com strategicmarketresearch.com. Major players – Nvidia, AMD, Intel, Apple, Amazon – have embraced chiplets to improve yields, costs and performance, leveraging 2.5D interposers and 3D stacking.

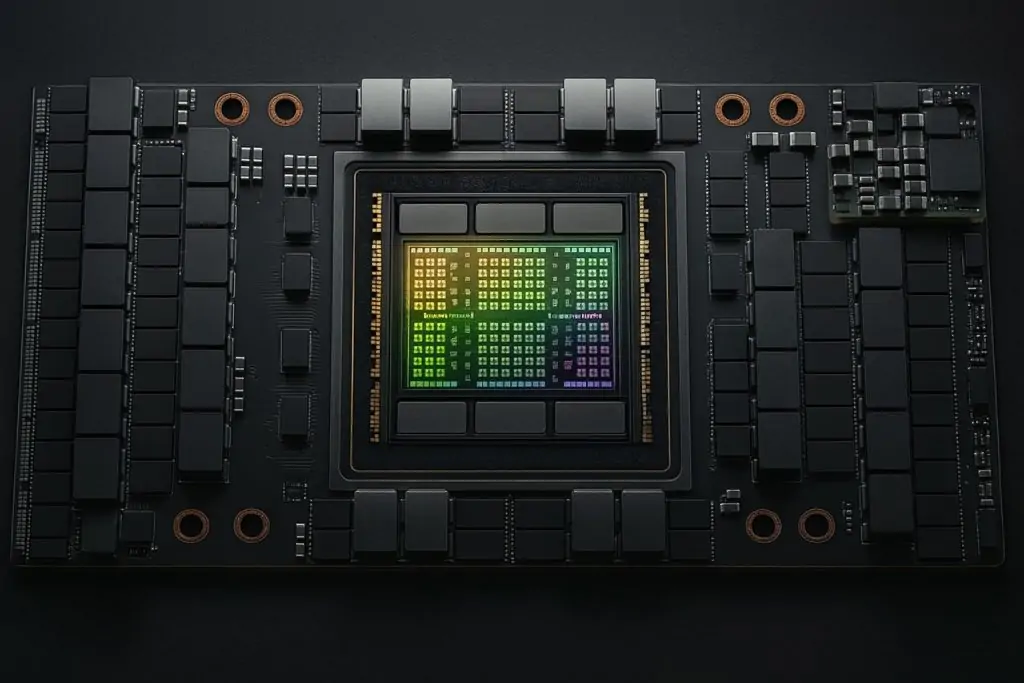

- HBM Integration Surges:High-bandwidth memory (HBM) stacked on-package has become a staple of AI and HPC chiplet designs (e.g. NVIDIA H100, AMD MI300), driving unprecedented demand. All three HBM suppliers (SK Hynix, Samsung, Micron) report 6–12 month lead times for HBM chips, extended further when advanced packaging (like CoWoS) is needed sourceability.com. HBM3 prices have jumped ~20–30% year-on-year and are expected to remain high through 2025 sourceability.com.

- Global Capacity Race: Foundries and OSATs worldwide are investing heavily to expand advanced packaging. TSMC leads with massive CoWoS capacity in Taiwan (targeting ~90k wafers/month by 2026) sourceability.com and new U.S. facilities for 3D SoIC and CoW packaging astutegroup.com. Intel is ramping its Foveros 3D and EMIB 2.5D capacity – a $7 billion advanced packaging fab in Malaysia comes online in 2024 newsroom.intel.com – and courting customers as TSMC runs full semiwiki.com eetimes.com. OSAT giants like ASE and Amkor are not far behind, with Amkor opening a $1.6 billion advanced packaging plant in Vietnam focused on chiplets and HBM integration tomshardware.com tomshardware.com.

- Shifting Market Share: Advanced packaging now makes up more than half of total semiconductor packaging revenue strategicmarketresearch.com strategicmarketresearch.com. TSMC has captured a growing slice at the high end (its InFO & CoWoS packaging contributed ~$5.7 billion in 2024 strategicmarketresearch.com), but OSATs still handle enormous volume. For instance, 53% of ASE’s packaging business is advanced packages strategicmarketresearch.com. NVIDIA alone is forecast to consume ~60% of global CoWoS capacity by 2026, mainly through TSMC, with the rest divided among AMD (~11%), Broadcom (~15%), and others via ASE, SPIL and Amkor astutegroup.com astutegroup.com. This highlights both the dominance of leading-edge foundries and the vital role of outsourced assemblers in meeting demand.

Introduction: Chiplets and 3D Integration Come of Age

Semiconductor design is undergoing a paradigm shift from giant monolithic chips toward chiplet-based and multi-die architectures. In a chiplet approach, a processor is disaggregated into multiple smaller dies (chiplets) that are later integrated in a package, rather than one large die. This strategy improves manufacturing yield and cost – smaller dies are easier to produce without defects – and allows mixing different process nodes and functions in one package astutegroup.com astutegroup.com. As traditional 2D scaling hits physical and economic limits, chiplets offer a practical path to keep improving performance and functionality astutegroup.com astutegroup.com.

Advanced packaging technologies are the linchpin making chiplet systems possible. Unlike classic packaging (wire-bonded single chips on a PCB), advanced methods include 2.5D integration – using an intermediate silicon interposer or bridge to fan-out connections between chiplets – and 3D integration, where dies are stacked vertically. Notably, TSMC’s CoWoS has become synonymous with 2.5D packaging: it uses a silicon interposer with dense through-silicon vias (TSVs) to connect multiple chips (logic, memory) as one, overcoming the density limits of standard substrates trendforce.com. TSMC SoIC (System-on-Integrated-Chips) represents 3D die-on-die bonding for high-density vertical stacking theregister.com. Competing approaches include Intel’s EMIB (Embedded Multi-die Bridge), which embeds tiny silicon bridges in the substrate to link dies without a large interposer – a cost advantage for big packages trendforce.com. Intel’s Foveros technology enables true 3D stacking of logic dies (as seen in Intel’s Meteor Lake processors), akin to SoIC. Samsung has introduced its own 2.5D platform called I-Cube (Integrate Chiplet on Interposer) for logic + HBM integration, and a 3D stacking tech (X-Cube) for stacking logic dies; these target high-performance computing chips as Samsung Foundry vies in this arena trendforce.com.

In essence, chiplets and advanced packaging go hand-in-hand – heterogeneous integration is now a key innovation front in semiconductors. This report delves into the current market landscape for chiplets and advanced packaging as of 2025, covering capacity and supply, adoption of high-bandwidth memory, market shares of key players, cost trends, and expert outlooks.

Global Capacity and Regional Expansion Efforts

The Asia-Pacific region dominates advanced packaging production, led by Taiwan and South Korea sourceability.com. TSMC (Taiwan) in particular has invested for years in advanced packaging capabilities on a massive scale. In 2024, TSMC’s CoWoS throughput was around 45,000–50,000 wafer packages per month, with plans to reach ~70k–80k per month by the end of 2025 design-reuse.com theregister.com. By late 2026, CoWoS capacity is expected to hit 90,000 wafers per month, which implies roughly a 50% CAGR expansion from 2022 levels sourceability.com. Even so, demand is so high that all new capacity is immediately booked – TSMC’s CoWoS lines have been effectively sold-out for years running, primarily filled by Nvidia, AMD and other AI chipmakers sourceability.com. TSMC’s CEO candidly noted in 2024, “It is not the shortage of AI chips, it is the shortage of our CoWoS capacity,” underscoring that packaging, not silicon, was gating AI hardware supply trendforce.com. To relieve bottlenecks, TSMC has been rapidly expanding facilities in Zhunan and Hsinchu in Taiwan and even floated plans for new advanced packaging sites (e.g. in Chiayi, Taiwan) trendforce.com trendforce.com.

Beyond Taiwan, TSMC is also geographically diversifying its packaging footprint under pressure from customers and governments. In the U.S., TSMC has announced plans to build advanced packaging capacity as part of its Arizona campus. Construction on a first U.S. packaging facility (focused on 3D SoIC and “CoW” wafer bonding technologies) is slated to begin by 2026, with completion before 2029 astutegroup.com. Notably, TSMC is expected to partner with a U.S.-based OSAT (likely Amkor’s Arizona operation) for the final substrate assembly steps astutegroup.com. This move will bring CoWoS/SoIC capabilities closer to North American clients like NVIDIA, aiming to boost supply chain resilience by 2030. South Korea is another key hub – aside from Samsung’s efforts (covered below), memory giants SK Hynix and Samsung perform in-house stacking for HBM and are ramping those back-end capabilities. Korea has also led in developing panel-level packaging (PLP) techniques for high volume; in 2024 it accounted for ~62% of global PLP capacity strategicmarketresearch.com strategicmarketresearch.com.

Intel, as both an IDM and an emerging foundry player, is making an aggressive push in advanced packaging. Intel’s 3D packaging tech (Foveros) and 2.5D tech (EMIB) were pioneered in-house for its own chips, but Intel is now offering these capabilities to foundry customers as well. The company has been building out major capacity: in Penang, Malaysia, Intel’s largest advanced packaging facility (710k sq ft cleanroom) was completed in late 2023, a $7 billion investment to quadruple Intel’s 3D packaging output newsroom.intel.com newsroom.intel.com. This new mega-fab is becoming operational in 2024 newsroom.intel.com and will substantially boost Foveros assembly for products launching 2025 onward. Intel is also expanding packaging operations in the U.S. – notably in New Mexico, where it has an advanced packaging hub (Fab 9) for Foveros/EMIB, and in Ohio and Arizona in conjunction with new fabs (ensuring on-site packaging for its foundry clients in the future) newsroom.intel.com newsroom.intel.com. Despite having “excess supply” available (relative to current external demand), Intel sees advanced packaging as a strategic offering. In 2025, Intel began actively courting companies whose CoWoS orders at TSMC couldn’t be met, inviting them to port designs to Intel’s Foveros lines semiwiki.com eetimes.com. TechInsights analyst Dan Hutcheson noted that Intel “built the capacity, but few have come so far because [Intel] has not been promoting it” eetimes.com. That is now changing – Intel’s marketing its packaging prowess, and even Nvidia and AMD have reportedly run test builds with Intel as a contingency eetimes.com. How many will shift remains to be seen, but Intel’s invitation underscores how tight TSMC’s capacity is and how critical advanced packaging has become.

Samsung has likewise entered the advanced packaging race to complement its foundry business. Samsung’s I-Cube (Interposer Cube) 2.5D technology and X-Cube 3D stacking were developed to integrate logic and memory for high-performance applications trendforce.com. While Samsung Foundry so far has fewer high-profile packaging clients (many customers needing HBM integration opt for TSMC or OSAT services), Samsung is ramping up. In 2023, it expanded advanced packaging lines in Onyang and Cheonan for HBM, and reportedly is planning new capacity in China (Suzhou) to bolster its packaging of memory products trendforce.com. Looking ahead, Samsung is preparing for HBM4 in 2025 and aims to offer 3D packaging services for next-gen memory stacks tweaktown.com. Internally, Samsung is also using advanced packaging for its own chips (for instance, its Exynos and AI chips can leverage I-Cube for HBM). Industry data suggests that by 2024, 63% of Samsung’s backend processes (for its chips) were already advanced packaging types strategicmarketresearch.com. This indicates Samsung is “eating its own cooking” to prove the technology as it courts more external business.

Traditional outsourced assembly and test providers (OSATs) are vigorously expanding to stay competitive. ASE Technology Holding – the world’s largest OSAT – has invested in high-end packaging through its Siliconware Precision Industries (SPIL) unit, which is actually qualified to perform CoWoS packaging in partnership with TSMC trendforce.com trendforce.com. ASE is also adding advanced packaging capacity at its Kaohsiung, Taiwan site, including fan-out and possibly 2.5D lines trendforce.com trendforce.com. Over 53% of ASE’s assembly business is now in advanced packages as it transitions away from legacy wirebond strategicmarketresearch.com. Meanwhile Amkor Technology, the second-largest OSAT, made a splash in late 2023 by opening a new cutting-edge packaging factory in Vietnam. This $1.6 billion facility spans 57 acres and 200,000 m² of cleanrooms, dedicated to “advanced multi-chiplet system-in-package with HBM memory” tomshardware.com tomshardware.com. The Amkor Vietnam plant is expected to handle high-density silicon interposer assembly and testing – crucially, it adds capacity outside Taiwan for clients who need 2.5D packaging. As Tom’s Hardware reported, “TSMC’s CoWoS capacity [being] sold out for quarters” bodes well for Amkor’s fab being busy as it ramps up tomshardware.com. Other notable OSAT moves include JCET (China’s top OSAT) offering 2.5D integration services, and SPIL (ASE’s subsidiary) securing deals to package certain custom AI chips (for example, part of Broadcom’s TPU orders) astutegroup.com.

Even memory-focused companies are investing in packaging to secure HBM supply. SK Hynix, the leading HBM supplier, announced a $1 billion investment in advanced packaging R&D and capacity – calling it the “future focus” for the next 50 years trendforce.com. SK Hynix is also building a large-scale HBM assembly plant in the United States (in Indiana) slated to start production in 2028 nomadsemi.com. Micron broke ground on a $7 billion HBM packaging facility in Singapore in 2025, aiming for volume production by 2027 nomadsemi.com. These projects, backed by government incentives (e.g. the US CHIPS Act), will create new regional capacity for stacking memory dies and possibly integrating them with logic. By late-2020s, we should see a less Taiwan-centric packaging network, with significant high-end capacity in Southeast Asia, the U.S., and even Europe (Intel also announced a new assembly/test plant in Poland, to open ~2027, which will handle advanced packages from its Ireland and German fabs) newsroom.intel.com newsroom.intel.com.

Despite these expansions, industry experts caution that adding packaging capacity is neither cheap nor fast. Building an advanced packaging plant can run in the billions of dollars (often $10B+ for a full-scale site) and take years to become fully operational sourceability.com. High-end packaging tools (for precision bonding, lithography for interposers, etc.) have long lead times themselves. TSMC noted it takes 6–9 months just to install and qualify a new CoWoS line after the equipment arrives medium.com. Additionally, key materials like ABF substrates and underfill resins have their own supply limitations. This means the capacity relief from new facilities (like those in 2024–2025) will be gradual. In the interim, all players are trying to optimize utilization and share load: TSMC, for example, is partnering with OSATs to offload some packaging steps and “complement TSMC’s capacity” for customers theregister.com. Intel is offering its idle capacity to others. And companies are redesigning some products to use slightly less complex packaging when possible (for example, Nvidia shifting some GPU models from CoWoS-S (silicon interposer) to CoWoS-L, which uses a laminate bridge and can be done by OSATs, thereby freeing up TSMC’s silicon interposer lines) reuters.com reuters.com. All these measures underscore the scramble to alleviate the packaging crunch in the short term.

Lead Times and Supply Constraints: The New Bottleneck

It’s increasingly clear that advanced packaging has become a critical chokepoint in the semiconductor supply chain. Whereas front-end wafer fab capacity was traditionally the limiting factor, today even when chips are fabricated, they might wait weeks or months in queue for packaging. In the current AI boom, many hyperscale orders are effectively “waiting on the package” – additional GPU dies can be produced, but they can’t be deployed until they’re integrated with HBM and substrates via CoWoS or similar processes sourceability.com sourceability.com.

The result has been extended lead times for packaged parts, especially those using HBM. Analysts report 6 to 12 month lead times for high-end AI GPU modules (like NVIDIA’s H100 or upcoming Blackwell) largely because of the packaging and memory integration backlog sourceability.com. In practical terms, a data center ordering new AI accelerators in mid-2024 might not receive them until mid-2025 or later. Smaller AI firms have in some cases been completely squeezed out, as major cloud providers snap up all available supply even at long lead times sourceability.com. TrendForce noted that some CoWoS customers were “demanding 2× capacity next year” and TSMC has had to allocate capacity carefully, reserving some slots for smaller ASIC startups so they’re not entirely shut out theregister.com theregister.com.

One specific pain point is the tight coupling of HBM memory supply with packaging capacity. An AI training engine typically requires several HBM stacks packaged alongside the logic die. HBM itself has limited suppliers (SK Hynix, Samsung, Micron) who have been running full-out. By Q4 2024, HBM3 chips had lead times of 6–12 months due to soaring orders sourceability.com. But even if one secures HBM chips, they must be assembled onto the GPU/accelerator. This is often done at the same advanced packaging facility (e.g. TSMC will take NVIDIA’s GPU wafer and Hynix’s HBM stacks and perform the CoWoS assembly). Thus, the slowest link defines delivery. In cases where HBM supply was available, packaging slots became the limiter, and vice versa. Customers effectively need to queue for both. As noted, some packaging processes can be shifted to alleviate this: for example, NVIDIA’s newer CoWoS-L approach uses less silicon-intensive methods, meaning OSATs like ASE can handle a portion of the work and relieve TSMC’s bottleneck reuters.com reuters.com. Jensen Huang confirmed that NVIDIA is moving its next-gen Blackwell GPUs largely to CoWoS-L, allowing TSMC to “transition CoWoS-S capacity to CoWoS-L” and expand total throughput reuters.com. This transition is “not about reducing capacity… It’s actually increasing capacity,” Huang said reuters.com. In short, Nvidia is working closely with TSMC on technology changes to improve output – a testament to how strategic packaging has become.

Another challenge is that advanced packaging capacity is geographically concentrated, which introduces risk. Over 80% of leading-edge packaging (2.5D/3D for AI/HPC) happens in Asia (Taiwan, South Korea, and some in China). A single disruption can have outsized impact. In April 2024, a 7.4 magnitude earthquake hit Taiwan, briefly halting several fabs and packaging plants sourceability.com. Even though production was restored quickly with minimal damage, the incident “underscores the fragility” of a supply chain so tightly clustered in one region sourceability.com. It fueled ongoing discussions about diversifying packaging locations (hence projects like TSMC Arizona, Intel Poland, SK Hynix US). Geopolitical moves also loom: U.S.–China trade tensions have led to export controls on advanced chip tech, and at one point in 2025 the U.S. administration mulled tariffs on imported semiconductors sourceability.com sourceability.com. If enacted broadly, such tariffs could penalize the typical global flow of chips (where, say, a memory made in Korea, packaged in Taiwan, then assembled into a system in Mexico, ends up in the U.S.) sourceability.com sourceability.com. For companies relying on Asia-based packaging, this adds uncertainty in cost and logistics.

Lead times are expected to remain long through at least 2025, given the time required to significantly expand capacity. Some relief may come in stages: e.g., TSMC’s monthly CoWoS output will likely surpass 70k units by late 2025 (from ~34k in 2024) seekingalpha.com, and memory makers plan to boost HBM volume in the second half of 2025. Indeed, by early 2025 there were signs that the worst crunch might slightly ease – reports indicated wait times for NVIDIA H100 GPUs came down from 8–11 months to around 3–4 months by late 2024 tomshardware.com. This was attributed in part to TSMC’s capacity jump and perhaps some double-ordering sorting out. However, any new wave of demand (for example, if generative AI adoption accelerates further or new models require even more memory) could tighten things again. Industry consensus is that packaging will remain a headline concern for the foreseeable future, toggling between periods of acute shortage and gradual catch-up.

HBM Adoption and Chiplet Design Trends

The rise of chiplets has gone hand-in-hand with the adoption of HBM (High Bandwidth Memory) as the preferred solution for feeding these compute engines with data. HBM is a specialized 3D-stacked DRAM that sits within the package, offering an order of magnitude higher bandwidth than traditional external memory. Initially used in a few niche products (like high-end GPUs and network chips), HBM in the 2020s became almost a necessity for top-tier AI accelerators. By 2024–2025, practically every leading AI chip or HPC GPU is built as a multi-chip module with HBM integrated via advanced packaging. NVIDIA’s flagship H100 GPU, for example, carries 6 stacks of HBM2E memory around the GPU die on a CoWoS interposer. AMD’s instinct MI250 and MI300 accelerators also use HBM (MI300A packs CPU, GPU, and HBM in one 3D package) theregister.com. Even some CPUs for data centers now offer HBM variants – for instance, Intel’s Sapphire Rapids had an HBM2e option to boost memory bandwidth, using EMIB to connect 4 CPU tiles with 4 HBM stacks on package.

This broadening adoption is reflected in production statistics: in 2024, 25% of all DRAM chips shipped were actually used as part of chiplet-based packages, according to one Semiengineering estimate astutegroup.com. (This presumably counts HBM and other memory die used in multi-die modules.) While that figure is striking, it underscores how AI/graphics demand has soaked up a big chunk of memory supply. HBM itself is still a small fraction of total DRAM bits (most DRAM goes into DDR4/DDR5 modules), but in revenue terms HBM is significant and growing fast. HBM3 and the new HBM3E standard are shipping as fast as SK Hynix and Samsung can produce them.

To integrate HBM in a design, chip architects have had to adopt heterogeneous integration techniques – essentially chiplet design. Rather than a GPU with huge on-die SRAM (which is inefficient), the solution is a GPU chiplet + HBM chiplets on an interposer. This delivers tremendous bandwidth (multi-terabytes per second) at acceptable power. The trade-off is complexity in packaging: HBM stacks are connected by thousands of micro-bumps to the interposer, requiring very fine pitch assembly and precise alignment. Yields can be a concern; multiple HBM stacks plus a large logic die mean many points of potential failure during bonding. That partly explains the cost (addressed in the next section) and why initially only the highest-value applications used HBM.

Now, however, the economics of AI justify HBM everywhere – the throughput gains outweigh the costs. By Q1 2025, over 58% of logic chipmakers surveyed said packaging innovation (like adding HBM, 3D stacks) was a “critical” factor for achieving bandwidth and power targets, second only to process node shrinks strategicmarketresearch.com strategicmarketresearch.com. Heterogeneous integration isn’t just an experiment; it’s a competitive necessity in high-end chips. As a result, we’re seeing new types of chiplets beyond just logic+HBM. For example, companies are exploring compute + cache chiplets (AMD’s 3D V-Cache stacks extra SRAM on CPUs using TSMC SoIC bonding), specialized accelerator chiplets on a package (Amazon’s AWS Trainium and Inferentia use multi-die approaches), and mixing analog/front-ends with digital blocks in advanced packages for 5G and automotive.

It’s worth noting that while in-house chiplet designs dominate (each company makes custom dies for their product), there’s interest in an open chiplet ecosystem. To date, the only widely used “open-market” chiplet is HBM memory – any chip designer can buy HBM stacks and integrate them astutegroup.com. In contrast, logic chiplets (CPUs, GPUs, etc.) are proprietary and not interoperable. Initiatives like UCIe (Universal Chiplet Interconnect Express) aim to standardize die-to-die interfaces so that mix-and-match chiplets could become possible in the future. As of 2025, none of the high-volume products are UCIe-compatible yet astutegroup.com, but momentum is building (industry consortia, DARPA programs, etc. are funding development). Many expect that in a few years, we might see third-party chiplet marketplaces – e.g. a company could buy a ready-made AI accelerator tile and integrate it with their own custom tiles. For now, though, the “chiplet economy” is mostly internal to big players who can invest in the whole multi-chip system design.

High Bandwidth Memory integration will continue to grow as AI models hunger for more memory bandwidth. HBM3E is slated to ramp in 2025 with even higher speeds (~1.2 TB/s per stack) semiconductor.samsung.com. Looking further, HBM4 is on the horizon by 2026–27, possibly increasing the number of DRAM layers (12-high or 16-high stacks) and even introducing logic-in-memory (a “base logic die” on advanced node underneath the DRAM layers) nomadsemi.com nomadsemi.com. Interestingly, that means memory vendors will themselves use chiplet concepts within HBM – essentially turning the base of the HBM stack into a logic chiplet (on 3–5 nm tech) that handles power management, ECC, RAS features for the DRAM above nomadsemi.com nomadsemi.com. This blurs the line between memory and logic, and will require tight collaboration between memory suppliers and foundries (indeed, reports say SK Hynix and Micron will outsource their HBM4 base die fabrication to TSMC’s 3 nm, while Samsung plans to use its own 4 nm for its HBM4 base die) nomadsemi.com nomadsemi.com. All of it further binds the ecosystem – by the time HBM4 arrives, one package might entail three different process nodes (the GPU on 3 nm, HBM base die on 5 nm, DRAM layers on specialized DRAM node). This heterogeneity must be married by advanced packaging. Companies that master this integration (and solve challenges like heat dissipation for stacks consuming kilowatts in a tiny area) will lead the pack.

Market Share: Foundries vs. OSAT in Advanced Packaging

The advanced packaging market is experiencing robust growth in size and in strategic importance. In 2024, revenue from advanced packaging services (including flip-chip, fan-out, 2.5D/3D etc.) reached roughly $40 billion, making up about 57% of the total semiconductor packaging market strategicmarketresearch.com strategicmarketresearch.com. By 2025 advanced packaging is on track to exceed 50% of all packaging by volume as well, signaling that the industry’s center of gravity has moved to these new techniques semiconductors.org. With this shift, the competitive landscape of who provides packaging is also changing – foundry players (like TSMC, Samsung, Intel) are now significant packaging providers, not just the OSAT companies of old.

TSMC stands out as the largest advanced packaging provider among foundries. Long known purely as a chip fab, TSMC’s integration services (CoWoS, SoIC, and its fan-out technology InFO) have grown into a multi-billion-dollar business line. In Taiwan’s 2024 stats, TSMC’s advanced packaging revenue (mainly from CoWoS and InFO) was about US$5.7 billion strategicmarketresearch.com. That is roughly 8–9% of TSMC’s total corporate revenue – a non-trivial share for what used to be a side offering. In fact, some estimates say chiplet-related production now accounts for ~15% of TSMC’s revenue astutegroup.com. TSMC has leveraged its position as a one-stop shop (fab + package) to capture business; many customers like the convenience and performance of tightly coupling the two steps. As EE Times noted, TSMC has been “very good at capturing customers in a single-stop sale – making both the wafers and the packages.” eetimes.com.

That said, OSAT companies still handle the majority of packaging in aggregate, especially for less cutting-edge packages and in sheer unit count. ASE Technology, after merging with SPIL, is by far the world’s largest packager overall. In 2024 ASE had nearly $19 billion in packaging and test revenue granitefirm.com, of which more than half is considered advanced packaging strategicmarketresearch.com. ASE’s share in high-end segments is significant, especially as it partners with TSMC on CoWoS subcontracting and runs its own fan-out lines. Amkor, the second-largest OSAT, had around $7 billion revenue and has been pivoting towards advanced SiP (its new Vietnam fab is evidence of that ambition). JCET of China and Powertech (PTI) of Taiwan are other key OSATs focusing on advanced nodes (PTI specializes in memory stacking, while JCET has introduced 2.5D packaging for domestic Chinese chips).

It’s useful to look at market share by segment: in the bleeding-edge 2.5D/3D segment (like interposer-based integration), TSMC commands the lion’s share thanks to CoWoS. One analysis by Morgan Stanley projected that in 2026, TSMC alone would fulfill about 80%+ of global CoWoS wafer demand (the rest going to a few OSATs) astutegroup.com astutegroup.com. NVIDIA, as the top consumer, is relying on TSMC for ~510k out of its 595k CoWoS wafer needs in 2026, with only ~80k (13%) allocated to OSATs (split between Amkor and ASE) astutegroup.com astutegroup.com. AMD similarly will source the bulk of its advanced packaging from TSMC (about 80k wafers) with a smaller portion at ASE/SPIL (25k wafers) astutegroup.com. Broadcom, interestingly, diversified a bit: out of 150k CoWoS wafers it needs for custom ASICs, ~90k are from TSMC and ~5k from ASE for Google’s TPU, plus possibly some from other OSATs for Meta’s chips astutegroup.com. This breakdown shows that for the most complex integration, foundry-based packaging (especially TSMC’s) currently dominates. OSATs are involved, but often in secondary roles or for slightly less complex variants (like CoWoS-L or smaller interposers).

In more mainstream advanced packaging (flip-chip of advanced nodes, fan-out wafer-level packaging, etc.), OSATs still have very strong positions. Flip-chip, for example, is ubiquitous for all kinds of chips and ASE, Amkor, PTI, and others run huge operations there. In 2024 flip-chip accounted for ~38% of advanced packaging revenue market.us, and companies like ASE lead in that category for consumer and automotive chips. Samsung and Intel primarily use their advanced packaging for their own or captive customer products at this stage, so their share in the merchant market is small – but that could change if Intel’s foundry business grows (Intel touts itself as the “leading producer of advanced packaging” by experience, having shipped 100+ products with 2.5D/3D packaging, though most were internal) intel.com. Samsung has done packaging for some customers who use Samsung foundry wafers, but it has not (yet) sold packaging as a standalone service at scale.

One big dynamic is that foundries and OSATs are now directly competing in areas that were once clear-cut. TSMC’s success essentially forced OSATs to move up the value chain (hence ASE investing in CoWoS capability). Conversely, Intel’s push to offer packaging may put it in competition or cooperation with OSATs. Intel has signaled willingness to outsource parts of packaging – for instance, it partnered with ASE for some steps of Ponte Vecchio’s assembly. TSMC too leverages OSATs for capacity (using companies like SPIL to augment CoWoS-L throughput) theregister.com. So rather than pure competition, the model is evolving to partnerships: foundries handle the most silicon-centric steps (like wafer-to-wafer bonding or making silicon interposers), then OSATs might do final assembly to substrate and testing. This hybrid approach can increase overall capacity and play to each side’s strengths.

Looking at market share numbers, Yole Research estimated that in 2023 advanced packaging made up 44% of the total IC packaging market (about $38 billion out of $86 billion) eenewseurope.com hardwarebee.com. Within that, TSMC was the single largest player by revenue in high-end packaging, while ASE was largest overall when all advanced formats are included. By 2025, advanced packaging revenue is projected around $47–50 billion eenewseurope.com. TSMC’s slice of that may increase given its expansions, but OSATs are not standing still. ASE, for instance, saw 21.6% YoY growth in its packaging revenue recently, driven by advanced packages strategicmarketresearch.com. Amkor likewise is expecting growth from its new capabilities. We also see entrants like Foxconn (better known for electronics assembly) eyeing semiconductor packaging – Foxconn’s CSO Chiang has been vocal about investing in advanced packaging tech, and the company even acquired a chip packaging facility in 2022.

In summary, the foundry vs. OSAT divide in advanced packaging is becoming blurry. Foundries currently dominate the ultra-complex 2.5D/3D integration for top-tier chips (especially AI/HPC), which is where much of the excitement (and revenue growth) lies. OSATs, however, still handle a huge share of advanced packaging in consumer, analog, and memory segments, and they are scaling up to take on more of the high-end work as well. The competition and collaboration between these sectors will likely shape how capacity is added and how accessible advanced packaging becomes to a broader range of chip designers in the future.

Pricing Trends and Cost Drivers

Advanced packaging and chiplet integration bring tremendous benefits, but they also introduce new cost structures. Generally, the cost per packaged device goes up significantly for 2.5D/3D packages compared to traditional single-die packages. Several factors drive this:

- Expensive Materials and Substrates: High density interposers and substrates are costly. A silicon interposer (like used in CoWoS-S) can cost on the order of $ hundreds per unit, and in some reports, very large interposers approach $1,000 each astutegroup.com astutegroup.com. These interposers are essentially silicon wafers with fine wiring – adding a big silicon piece under your chips naturally adds cost. Even advanced organic substrates (for CoWoS-L or similar) have many layers and require ABF (Ajinomoto Build-up Film) which saw shortages and price hikes in recent years. In 2024, interposer substrate costs were rising ~8.4% due to material constraints strategicmarketresearch.com.

- Complex Assembly Process: 2.5D/3D packaging involves multiple steps like die attachment, underfilling, TSV formation, and possibly wafer bonding. Each step needs precise tools and can lower yield. For example, 3D TSV packaging costs were estimated to have increased ~7.2% in one year due to the added complexity and need for more process control strategicmarketresearch.com. Newer techniques like hybrid bonding (direct copper-to-copper bonding between dies) promise better density, but the equipment (hybrid bonders, requiring extremely flat surfaces and cleanrooms) can cost millions each – roughly 3× the cost of standard thermocompression bonders nomadsemi.com nomadsemi.com. The total cost of ownership for these processes includes things like extra CMP (planarization steps) and more stringent cleanroom standards, all of which drive up cost nomadsemi.com.

- Yield Considerations: In a chiplet or stacked design, yield economics are nuanced. You may get better yield per die by keeping them smaller, but when you integrate, the yield of the package is the product of yields of all components. If any one chiplet or HBM stack is bad, the whole module might be scrapped or require rework. For HBM, stacking 8 DRAM dies means even a 95% yield per die results in only ~66% yield for the stack nomadsemi.com. Memory makers mitigate this by adding spares in HBM and doing known-good-die testing. Still, overall packaging yields for complex multi-die systems can be in the 80–90% range, lower than single-die. That yield loss effectively raises cost per good unit (the cost of discarded components must be amortized). Some manufacturers report using AI for adaptive testing and binning to improve yield and catch problems earlier astutegroup.com astutegroup.com, but it remains a significant factor.

- HBM Pricing Premium: HBM is one of the most expensive components in these systems. Prices for HBM have been rising with demand. As noted, HBM3 saw 20–30% YoY price increases entering 2025 sourceability.com. A single 16 GB HBM2e stack was roughly $200–$250 in 2022; HBM3 16 GB or 24 GB stacks could cost more. A module like NVIDIA’s H100 carries many HBM stacks – memory alone could be $1,000+ of the BOM cost. When HBM supply is tight, buyers may even pay over list price or pay expedite fees. This directly feeds into the cost of packaged AI accelerators and is often passed on to end customers (e.g., the steep prices of AI server GPUs). TrendForce expects HBM contract prices to remain on an upward trend through 2025 due to chronic undersupply sourceability.com.

- Testing and Yield Recovery Costs: Multi-chip packages require more intensive testing (Known Good Die testing before assembly, then testing the assembled module). Burn-in and validation of HBM-integrated devices is complex – you have to test memory and logic together at high speeds. Testing time per unit tends to be longer, and high-end testers are expensive equipment (Advantest or Teradyne testers for HBM3 are cutting-edge and not cheap). All this adds a few more dollars to each device’s cost just for test. Additionally, if a module fails partially, companies may attempt rework (for instance, replacing a bad HBM stack – which requires careful re-balling and can be low-yield). Such yield recovery attempts, while sometimes worthwhile for very costly modules, add labor and cycle time.

- Power/Thermal Management Costs: While not a direct packaging cost, designing these packages often means adding costly thermal solutions (exotic heatsinks, liquid cooling for AI systems) because the power density is so high. For chiplets, sometimes interposer size is driven by needing to space out hot chips or include thermal vias, etc., which again can influence cost. In extreme cases, advanced cooling like built-in microfluidic channels are being researched for future 3D stacks astutegroup.com. These aren’t mainstream yet in 2025, but any added complexity to manage heat can indirectly raise packaging costs or at least the total system cost.

On the flip side, cost per transistor at advanced nodes has skyrocketed, so chiplets help avoid that. By using chiplets, companies save money by mixing nodes (e.g., put only critical IP on 5 nm, keep other IP on cheaper 16 nm die) and by improving yield (many small dies instead of one huge die that might have low yield). These savings can offset the packaging premium to an extent. AMD’s CEO has often cited chiplets as a way to deliver more performance per dollar – for example, the chiplet design in EPYC server CPUs let AMD use chiplets from a mature node for I/O, saving a lot of cost, while only the cores are on the latest node. Similarly, in GPUs, splitting a large die into smaller tiles could eventually be more cost-effective if packaging can be done at scale cheaply. As of 2025, though, very few GPUs are disaggregated (most still one big die + HBM), partly because the packaging cost and latency of multi-GPU tile links have been concerns. But that’s changing: we expect to see more tiled GPU designs (like Intel’s Ponte Vecchio had 47 chiplets, and NVIDIA hinted future GPUs may be multi-tile).

Pricing trends for advanced packaging services themselves (what foundries/OSATs charge) are not publicly detailed, but industry reports suggest that assembly and test cost as a proportion of total chip cost has been rising for high-end products. For a typical smartphone SoC, packaging might be under 10% of the total chip cost. For an AI GPU, packaging (including HBM) can exceed 50% of total module cost. The sustained high demand means neither foundries nor OSATs have had pressure to cut prices – if anything, there have been premiums. TSMC reportedly charges a premium for CoWoS capacity, and clients are willing to pay to secure slots given the shortage. We have also seen long-term agreements or pre-payments; for instance, some of the large AI firms have prepaid TSMC to reserve CoWoS capacity through 2024–25, which is atypical in the packaging realm (similar to how fabs require prepayment for wafer capacity).

Looking ahead, cost drivers might moderate if new technologies hit production: e.g., moving to larger panels for fan-out could bring economies of scale (Samsung and ASE are working on panel-level packaging to reduce cost for certain applications). Also, automation and yield learning will improve over time, shaving a few percent off costs here and there. But any introduction of next-gen tech (like hybrid bonding for HBM5 in a few years) could again push costs up initially. For now, customers seem willing to bear high packaging costs because the end-market value of AI and advanced chips justifies it – the ROI of a faster AI accelerator is so high that even very pricey packaging is an acceptable expense. As one executive summarized, “packaging is no longer an afterthought – it’s the front line of innovation” and companies are treating it as such strategicmarketresearch.com strategicmarketresearch.com, allocating budget to get the performance gains.

Industry Perspectives and Latest Developments

Industry leaders routinely stress how crucial chiplet and packaging technologies have become for the future of semiconductors. NVIDIA’s CEO Jensen Huang has been particularly vocal: he famously declared “Moore’s Law is dead” at 2022’s GTC conference, suggesting that continued scaling will come from “advanced chip-on-wafer-on-substrate technologies” (i.e. CoWoS) and not just transistor shrinkage x.com. By early 2025, Huang emphasized that NVIDIA’s appetite for advanced packaging was only growing – “We’re not reducing capacity… [we’re] actually increasing capacity” by shifting to newer CoWoS methods reuters.com. He also pointed out that despite quadrupling packaging capacity in two years, it remains a bottleneck for NVIDIA, as demand is insatiable reuters.com. This underscores a common view: packaging is now as strategic as wafer fabs for companies like NVIDIA.

TSMC’s leadership also routinely highlights advanced packaging. In an April 2024 earnings call, TSMC’s CEO C.C. Wei and his team noted they were “fully committed” to investing in advanced packaging to meet huge cloud AI demand theregister.com. TSMC has had to assure analysts it will allocate capacity fairly (balancing big clients vs. smaller ones) and mentioned leveraging OSAT partners to help fulfill needs theregister.com. Mark Liu, TSMC’s chairman, brought CoWoS to the spotlight with his comment about CoWoS shortages, which actually helped drive government awareness and support for packaging initiatives trendforce.com. Taiwan’s government, for example, started including advanced packaging in its definition of critical semiconductor tech for national support programs post-2024.

Analyst firms like Yole and TrendForce have dubbed advanced packaging “the next battleground” in the semiconductor value chain digitimes.com. A TrendForce news piece in 2024 noted that “from foundries and memory manufacturers to OSATs, all are actively involved in research and capacity expansion” for advanced packaging trendforce.com. There’s a sense that whoever leads in packaging may have an edge in capturing future high-performance chip markets. This is partly why Intel, despite execution challenges in other areas, is emphasizing its packaging prowess. As EE Times reported, Intel openly invited others to its Foveros lines because TSMC couldn’t meet all demand semiwiki.com. Intel’s messaging, backed by folks like Rahul Goyal (Intel VP of Packaging), is that Intel has “an embarrassment of riches” in packaging capacity that they’re ready to use semiwiki.com. Skeptics point out that getting customers to switch is non-trivial – trust in execution is a hurdle, given some past missteps like Intel’s delayed Ponte Vecchio GPU which heavily relied on advanced packaging semiwiki.com. Still, if Intel’s bet pays off, it could establish a unique differentiator for Intel Foundry Services.

From a technology perspective, one exciting development is the transition to CoWoS-L and similar bridge-based packaging as a complement to interposers. Ming-Chi Kuo, a well-known analyst, noted NVIDIA’s shift to CoWoS-L for Blackwell and suggested suppliers of CoWoS-S might be impacted reuters.com. The industry is watching how CoWoS-L (which uses a laminate with bridge chips – essentially a beefed-up version of Intel’s EMIB concept) performs in volume. If it delivers near the interposer performance but with easier manufacturing, it could relieve some strain and be a more cost-effective way to integrate HBM. TSMC and others are also looking at fan-out on substrate approaches for AI chips (sometimes dubbed InFO_oS), though so far CoWoS reigns for top bandwidth needs.

There’s also a lot of R&D in 3D integration going on: for instance, TSMC’s SoIC was used by AMD to stack cache on Ryzen CPUs (3D V-Cache) with great success in 2022–2023. AMD’s CTO Mark Papermaster has said 3D stacking will be central to their roadmap, allowing them to add specialized silicon (like cache, or chiplet accelerators) on top of main processors. We also see experimentation like TSMC’s WoW (Wafer-on-Wafer) stacking used in some niche products, and Intel’s planning for their “Foveros Omni” and “Foveros Direct” technologies to push denser 3D integration by 2025–2026. These could enable things like mixing DRAM cache die on CPU tiles more routinely.

From an analyst commentary standpoint, many note the economics of chiplets are as compelling as the technology. A recent market report projected the chiplet market (including all components and services) to grow at an astonishing ~70% CAGR to reach $50+ billion by 2032 coherentmarketinsights.com. While that kind of number might be optimistic, it reflects belief that chiplets will permeate much of semiconductor design, not just high-end. If that’s true, advanced packaging will likewise become a universal requirement. Executives from companies like ASE have said they expect advanced packaging to account for an ever-greater portion of their revenue mix and that they are investing accordingly in tools and talent. ASE’s CEO Tien Wu is known for saying packaging is the “last mile” of Moore’s Law – essentially, that integration will pick up where transistor scaling leaves off, enabling continued improvements.

Finally, it’s worth mentioning government and policy support. The U.S., Europe, Japan, and others have launched initiatives to bolster packaging capabilities domestically, recognizing it as a strategic gap. The US CHIPS Act explicitly includes funding for advanced packaging institutes and factories. In 2025, for example, the U.S. DoD was funding projects on open chiplet standards and secure packaging, and companies like Intel, IBM, and Qualcomm participated in those. India is another player to watch – as part of its semiconductor mission, India is trying to establish OSAT facilities (some lines are being set up, though mostly for traditional packaging initially). The goal for many nations is to have at least some capacity for advanced packaging of critical chips (especially for defense or key industries) onshore.

In conclusion, chiplets and advanced packaging have moved to center stage in the semiconductor industry by 2025. The technology has proven its worth in enabling the AI computing boom, and now the challenge is scaling up capacity and driving down cost. As we’ve seen, major foundries and OSATs are pouring capital into this area, and new partnerships are forming across the ecosystem. While short-term supply constraints and high costs persist, the trajectory is clearly toward wider adoption of heterogeneous integration across nearly every computing segment – from cloud AI down to edge devices and even consumer electronics. As one industry CEO put it, “we’re entering the chiplet era” – and mastering advanced packaging will be key to determining who leads and who lags in this new era of semiconductors eetimes.com eetimes.com.

Sources:

- M. Lavesque, “AI chip shortages deepen amid tariff risks,” Sourceability Industry Updates, Jun. 2, 2025. sourceability.com sourceability.com

- Astute Analytics, “Chiplets: Unpacking the Future of Advanced Electronics Production,” Jul. 4, 2025. astutegroup.com astutegroup.com

- J. Breeden II, “TSMC fully booked on advanced packaging until 2025,” The Register, May 7, 2024. theregister.com theregister.com

- W-Y. Lee, “Nvidia CEO says its advanced packaging technology needs are changing,” Reuters, Jan. 16, 2025. reuters.com reuters.com

- A. Shilov, “Amkor Builds $1.6 Billion Advanced Chip Packaging Factory,” Tom’s Hardware, Oct. 11, 2023. tomshardware.com tomshardware.com

- Strategic Market Research, “Semiconductor Packaging Industry Statistics 2024 – Key Insights,” Jun. 2025. strategicmarketresearch.com strategicmarketresearch.com

- TrendForce News, “The Era of Heterogeneous Integration: Who Shall Dominate Advanced Packaging?,” Mar. 18, 2024. trendforce.com trendforce.com

- S. Shieh, “Advanced Packaging Demand Soars: Nvidia Secures 60% of CoWoS Capacity,” Astute Group News, Aug. 4, 2025. astutegroup.com astutegroup.com

- M. LaPedus, “Packaging Firms Post Mixed Results In Q4 ’24,” Semiconductor Ecosystem (Substack), Feb. 2025. strategicmarketresearch.com strategicmarketresearch.com

- C. Sturman, “U.S. Chip Tariffs: Impacts on the U.K. And Beyond,” TechWorks, Aug. 22, 2025. sourceability.com sourceability.com