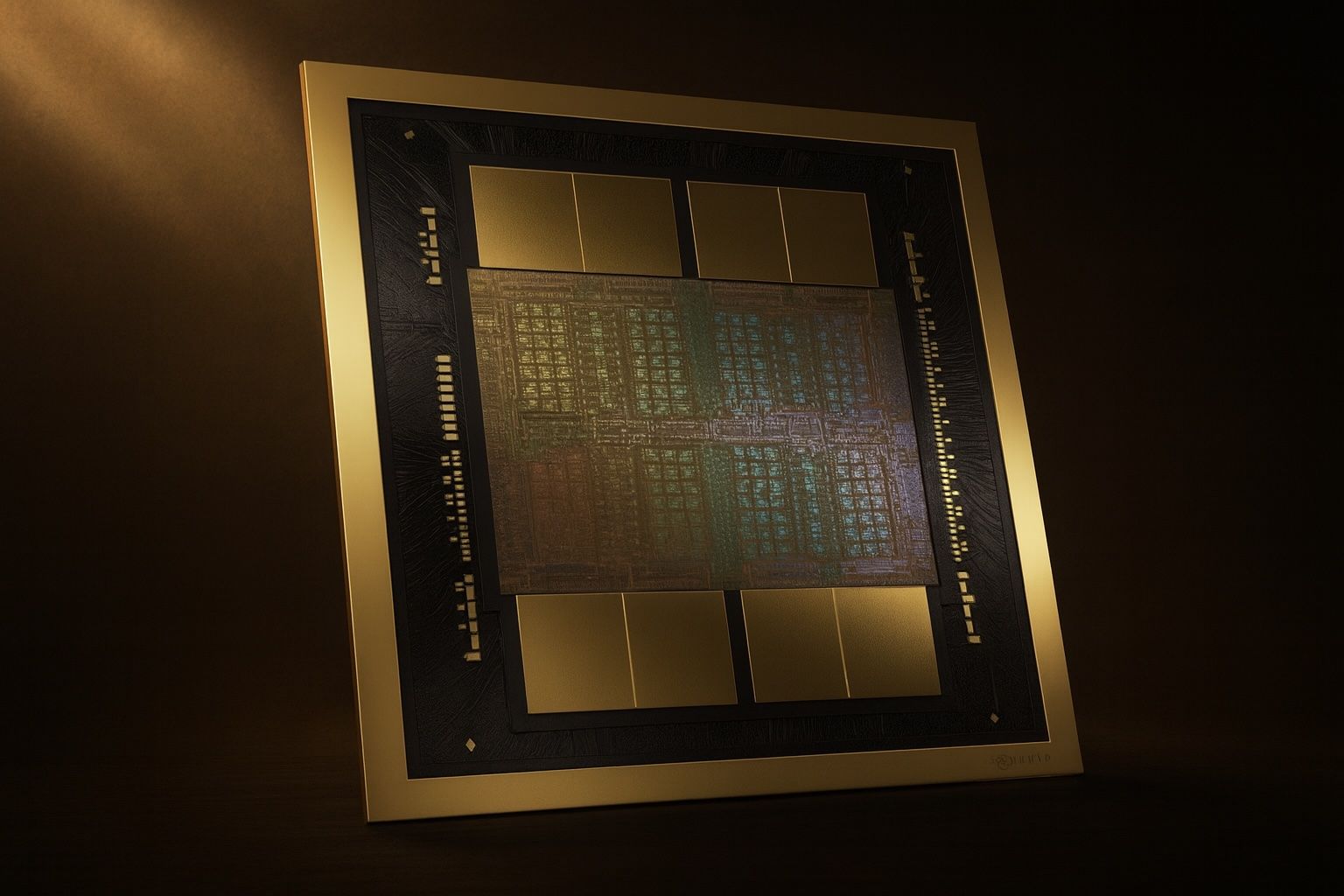

- NVIDIA Blackwell B200: 180 Go de mémoire HBM3e par GPU et jusqu’à 8 To/s de bande passante mémoire, dans une architecture multi‑puce.

- Le B200 affiche environ 4,5 PFLOPS en FP16/BF16 et 9 PFLOPS en FP8, avec 9 PetaOps INT8 en inférence, et promet environ 3× d’entraînement et 15× d’inférence par rapport au H100.

- Un DGX B200 typique comprend 8 GPU B200 et une consommation d’environ 14,3 kW, soit ~1,5 kW par GPU, avec 900 Go/s de bande passante par lien NVLink et 1,8 To/s total sur le GPU.

- AMD Instinct MI350X/MI355X (CDNA4, TSMC N3P) intègrent 288 Go de mémoire HBM3e et jusqu’à 8 To/s de bande passante, avec 185 milliards de transistors, et MI355X peut atteindre 1 400 W alors que MI350X tourne autour de 1 000 W.

- La série MI350 revendique jusqu’à 4× plus de calcul IA et jusqu’à 35× plus de débit d’inférence par rapport au MI300, grâce au FP4/FP6 et à l’empilement 3D.

- Google TPU v6e (Trillium) délivre 918 TFLOPS BF16 par puce, 32 Go de mémoire par puce et 1,6 To/s de bande passante, avec des pods de 256 puces et le SparseCore de troisième génération.

- Un pod TPU v6e standard réunit 256 puces sur 32 hôtes, atteignant théoriquement 234,9 PFLOPS BF16 et plus de 1 exaOP/s en INT8, avec 8 To de mémoire HBM par pod.

- Disponibilité: NVIDIA DGX B200 est en production fin 2024 et déployé via DGX Cloud, avec un prix par GPU estimé entre 30 000 et 40 000 $, et le module Grace+Blackwell GB200 prévu en 2025 autour de 60 000–70 000 $ par module, disponibilité cloud sur AWS, Azure, GCP et Oracle.

- La disponibilité des MI350X/MI355X est prévue en 2025, avec expéditions limitées dès 2025 et déploiement en volume fin 2025, dont El Capitan du DOE et des tests par Azure et Meta.

- TPU v6e est disponible sur Google Cloud via Vertex AI et ct6e-standard, prend en charge TensorFlow et JAX, PyTorch via PyTorch XLA, et peut être configuré de 1 puce à 256 puces par pod, avec une interconnexion multi‑pod via des Titanium IPUs.

La course à la suprématie des accélérateurs d’IA a atteint son paroxysme en 2024–2025. NVIDIA, AMD et Google ont chacun dévoilé du matériel de pointe visant à répondre à la demande explosive de l’IA générative, des grands modèles de langage (LLM) et du calcul haute performance (HPC). Le nouveau GPU Blackwell B200 de NVIDIA, la série Instinct MI350 d’AMD et le TPU v6e “Trillium” de Google sont tous présentés comme des puces révolutionnaires, chacune repoussant les limites en matière d’architecture, de performance et d’efficacité. Ce rapport propose une comparaison approfondie de ces trois accélérateurs – couvrant leurs architectures, leurs performances brutes (FLOPS, bande passante mémoire, etc.), leur efficacité énergétique, leurs écosystèmes logiciels, des benchmarks en conditions réelles, des scénarios de déploiement, et plus encore. Nous mettons également en avant des commentaires d’experts et les développements récents, et jetons un œil aux feuilles de route de prochaine génération que chaque entreprise poursuit.

Dans ce duel de titans de l’IA, le GPU Blackwell de NVIDIA promet 3× de gains en entraînement et 15× en inférence par rapport à son prédécesseur nvidia.com, le MI350 d’AMD (architecture CDNA4) affiche jusqu’à 4× plus de puissance de calcul IA et 35× plus de rapidité en inférence IA que la génération précédente tomshardware.com smbom.com, et le TPU v6e de Google offre un bond de 4,7× en calcul maximal ainsi qu’un doublement de la mémoire et de la bande passante d’interconnexion par rapport à ses TPU de génération précédente cloud.google.com cloud.google.com. Ci-dessous, nous analysons chaque solution et comparons leur positionnement dans le paysage concurrentiel de l’accélération de l’IA.

NVIDIA Blackwell B200 – Architecture et performances

Innovations architecturales : la NVIDIA Blackwell B200 est le fleuron de la dernière architecture GPU de NVIDIA, succédant à la Hopper H100. Blackwell introduit une conception multi-puces (chiplet), une capacité mémoire nettement supérieure, de nouveaux formats mathématiques en basse précision, et des interconnexions plus rapides. Un seul GPU B200 est doté de 180 Go de mémoire HBM3e (contre 80 Go sur la H100), offrant jusqu’à 8 To/s de bande passante mémoire exxactcorp.com exxactcorp.com. Cette mémoire massive (180 Go par GPU) permet d’entraîner des modèles plus grands ou d’utiliser des tailles de lot plus importantes, un avantage clé qui a contribué à un entraînement de modèles ~57 % plus rapide sur certaines charges de travail de vision par rapport aux GPU H100 lightly.ai lightly.ai. Blackwell double également le débit des cœurs tenseurs pour les calculs IA : il prend en charge les nouvelles précisions FP4 et FP6 (en plus de FP8/FP16/TF32), utilisant un moteur Transformer de seconde génération pour exploiter dynamiquement la basse précision et accélérer les calculs developer.nvidia.com developer.nvidia.com. En sacrifiant une partie du débit FP64 (crucial pour le HPC traditionnel) au profit d’une augmentation massive des performances des cœurs tenseurs en basse précision, le B200 atteint plus de 2× plus de débit TF32/FP16/INT8 que Hopper exxactcorp.com exxactcorp.com. En fait, le B200 peut effectuer 18 PFLOPS d’opérations tenseur FP4 (pic) – une nouvelle frontière rendue possible par ses cœurs FP4 exxactcorp.com. La puce est fabriquée sur un nœud de procédé de pointe (probablement TSMC 4nm ou 3nm) et dispose d’un budget de transistors énorme (NVIDIA n’a pas communiqué publiquement le nombre de transistors, mais il devrait largement dépasser les 80 milliards de la H100). Le refroidissement et l’alimentation sont des considérations majeures – les cartes B200 pour centres de données sont proposées en modules au format SXM et peuvent consommer environ 1,5 kW chacune en charge (estimations basées sur un système DGX 8× B200 consommant ~14,3 kW) nvidia.com nvidia.com.

Performance et benchmarks : En termes de performance brute, le Blackwell B200 est un monstre. Il offre environ 4,5 PFLOPS en FP16/BF16 et 9 PFLOPS en FP8 pour le calcul tensoriel, soit plus du double de la génération précédente exxactcorp.com. Pour l’inférence, son débit INT8 atteint environ 9 PetaOps (contre ~4 PetaOps sur le H100) exxactcorp.com, et la nouvelle capacité FP4 double encore le débit pour certains modèles basés sur les Transformers developer.nvidia.com. Les résultats des benchmarks en conditions réelles confirment ces spécifications. Lors des derniers tests MLPerf, les systèmes équipés de GPU Blackwell ont battu des records. Un serveur DGX B200 à huit GPU a atteint 3,1× plus de débit sur un benchmark d’inférence Llama-2 70B chatbot comparé à un système H200 (Hopper-refresh) à huit GPU developer.nvidia.com. Dans un scénario d’inférence massif Llama 3.1 (modèle à 405 milliards de paramètres), le superchip Grace+Blackwell GB200 de NVIDIA (combinant 72 GPU Blackwell avec 36 CPU Grace dans un cluster) a délivré jusqu’à 3,4× la performance par GPU d’un système basé sur Hopper developer.nvidia.com developer.nvidia.com. Au niveau du système, cette configuration GB200 a atteint une augmentation stupéfiante de 30× du débit global sur le test du modèle 405B, grâce à un plus grand nombre de GPU et au réseau NVLink Switch qui les relie developer.nvidia.com. Même sur des tests à plus petite échelle, les premiers utilisateurs rapportent des gains solides : Lightly.ai a comparé le B200 au H100 sur des charges réelles et a constaté que le B200 était environ 57 % plus rapide sur les tâches d’entraînement intensives en GPU (par exemple, l’entraînement de vision par ordinateur YOLOv8) et ~10 % plus rapide sur les tâches d’inférence LLM de taille moyenne lightly.ai lightly.ai. À noter, la grande mémoire du Blackwell (180 Go) lui permet de traiter des batchs plus importants pour améliorer le débit d’entraînement, et sa nouveauté implique que les logiciels d’inférence sont encore en cours d’optimisation – l’accélération d’environ 10 % sur les LLM devrait s’accentuer à mesure que les bibliothèques CUDA mûrissent lightly.ai. NVIDIA elle-même affirme que le DGX B200 offre 3× les performances d’entraînement et 15× les performances d’inférence des systèmes DGX H100 dans les workflows de bout en bout nvidia.com, mettant en avant la force particulière de Blackwell en inférence (probablement grâce à l’accélération FP4 et à d’autres optimisations pour les modèles de transformeurs). Pour les performances de type HPC en double précision (FP64), Blackwell se maintient autour de 30–40 TFLOPS FP64 (similaire au H100) exxactcorp.com sur les opérations vectorielles, bien que le débit des cœurs tensoriels FP64 soit réduit par rapport à Hopper exxactcorp.com – ce qui indique l’accent stratégique de NVIDIA sur les charges de travail IA plutôt que sur le HPC classique pour cette génération.

Efficacité énergétique : Malgré ses performances brutes supérieures, la Blackwell B200 vise à être beaucoup plus économe en énergie pour les tâches d’IA. NVIDIA annonce une amélioration de 15× des performances d’inférence par système (DGX B200 vs DGX H100) pour une enveloppe de puissance similaire nvidia.com. Les gains architecturaux (comme la prise en charge optimisée de la sparsité et le Transformer Engine) contribuent à bien plus de performances par watt sur les charges de travail IA. Les GPU Blackwell exploitent également les interconnexions NVLink de 5e génération (900 Go/s par lien GPU, 1,8 To/s au total sur le GPU) exxactcorp.com, réduisant les goulets d’étranglement liés au déplacement des données et la charge du CPU. Cela, combiné à une meilleure gestion de l’énergie, permet des économies d’énergie importantes pour des tâches équivalentes. Par exemple, une analyse a montré que Blackwell offrait une amélioration de 25× de l’efficacité énergétique sur certaines tâches d’inférence IA par rapport à son prédécesseur adrianco.medium.com. Cela dit, la consommation électrique absolue reste élevée ; l’appétit de la B200 (jusqu’à ~1,4 kW par GPU sur des charges lourdes) nécessite un refroidissement avancé. NVIDIA propose des variantes à refroidissement par air et par liquide selon les besoins de déploiement. L’angle performance-par-TCO est crucial – même si chaque GPU B200 est coûteux et énergivore, le débit qu’il fournit peut réduire le nombre total de serveurs nécessaires. NVIDIA souligne que concentrer plus de performances dans chaque rack (via des GPU puissants comme la B200) réduit au final le coût et la consommation par unité de travail, en particulier pour les déploiements à grande échelle tomshardware.com tomshardware.com. Cela correspond à ce que recherchent les utilisateurs professionnels : plus de densité de calcul IA pour maximiser l’efficacité des centres de données.

Logiciel et écosystème : Le plus grand avantage de NVIDIA reste sa pile logicielle. Le Blackwell B200 est entièrement pris en charge par l’écosystème logiciel CUDA et NVIDIA AI dès le premier jour. Les développeurs peuvent exploiter les bibliothèques optimisées de NVIDIA (cuDNN, TensorRT, CUDA-X APIs, etc.) et des frameworks comme TensorRT-LLM pour l’inférence LLM accélérée developer.nvidia.com. En fait, la capacité FP4 de Blackwell est accessible via TensorRT et de nouveaux outils de quantification, permettant aux modèles de fonctionner en précision FP4 avec une perte de précision minimale – un facteur clé dans ces énormes gains d’inférence developer.nvidia.com. L’entraînement multi-GPU à grande échelle est rendu possible par le tissu NVLink Switch (NVSwitch) qui connecte tous les GPU d’un serveur, voire entre serveurs (dans le pod GB200), en un cluster à haute vitesse. Des fonctionnalités comme Multi-Instance GPU (MIG) sont également prises en charge, permettant de partitionner un B200 en jusqu’à 7 instances GPU isolées (chacune avec ~23 Go) pour servir plusieurs tâches exxactcorp.com. Du point de vue du déploiement, les GPU Blackwell sont disponibles dans les propres systèmes DGX B200 de NVIDIA et les cartes HGX pour les fabricants de serveurs OEM. Les principaux fournisseurs de cloud déploient également des instances basées sur Blackwell – NVIDIA a annoncé une large disponibilité auprès des principaux fournisseurs de cloud en 2024 developer.nvidia.com. Cela signifie que les entreprises peuvent accéder aux performances du B200 soit sur site, soit dans le cloud avec une relative facilité. Le PDG de NVIDIA, Jensen Huang, décrit souvent leur approche plateforme comme offrant « la pile complète, du silicium au logiciel » pour accélérer l’IA. Blackwell en est un exemple parfait – ce n’est pas seulement une puce, mais fait partie d’une plateforme IA unifiée avec logiciels et services (comme NVIDIA AI Enterprise, les frameworks NeMo pour LLM, et les intégrations DGX Cloud) nvidia.com nvidia.com. Cet écosystème robuste donne à NVIDIA un positionnement concurrentiel fort, car les développeurs peuvent facilement transférer des modèles et des compétences des GPU précédents (comme le H100) vers le nouveau Blackwell avec un minimum de friction.

AMD Instinct MI350 (CDNA 4) – Architecture et performances

Innovations architecturales : la série Instinct MI350 d’AMD représente la réponse d’AMD à Blackwell – une famille de GPU pour centres de données basée sur la nouvelle architecture CDNA 4 et la technologie avancée de chiplet/empilement 3D. Présentés par la PDG Dr. Lisa Su au Computex 2024, les puces MI350 sont fabriquées selon le processus TSMC de classe 3 nm (N3P) et intègrent environ ~185 milliards de transistors dans une conception multi-puces smbom.com. Comme son prédécesseur (série MI300), le MI350 utilise l’intégration 3D pour combiner des dies de calcul et de la mémoire HBM empilée. Le fleuron MI355X et sa version refroidie par air MI350X embarquent une impressionnante mémoire HBM3e de 288 Go, avec une bande passante totale allant jusqu’à 8 To/s tomshardware.com tomshardware.com. C’est 1,5× la capacité mémoire du B200 de NVIDIA (180 Go), un fait qu’AMD met en avant – le MI355X offre 60 % de capacité HBM en plus que les GPU B200/GB200 de NVIDIA (288 Go contre ~180 Go) tomshardware.com. Le sous-système mémoire est non seulement plus grand mais aussi plus rapide, grâce à la HBM3e et à un bus mémoire élargi. La série MI350 introduit également la prise en charge matérielle de nouveaux formats flottants 4 bits et 6 bits (FP4 et FP6), à l’image de l’approche de NVIDIA, pour accélérer l’inférence IA. Les ingénieurs d’AMD ont doublé les capacités de calcul matriciel : l’architecture CDNA 4 inclut des Matrix Cores optimisés pour la basse précision. Notamment, AMD a choisi de réduire le débit FP64 sur le MI350 par rapport au MI300X, réallouant du silicium aux unités dédiées à l’IA – les performances matricielles FP64 sont à peu près divisées par deux, tandis que les opérations vectorielles FP64 ne baissent que d’environ 4 % d’une génération à l’autre tomshardware.com tomshardware.com. Cela indique un virage stratégique vers les charges de travail IA, à l’image de la stratégie de NVIDIA. Le die GPU du MI350X est uniquement dédié au calcul (contrairement au MI300A qui combinait CPU+GPU), car AMD a abandonné l’approche APU pour cette génération afin de se concentrer sur des conceptions GPU seules pour une évolutivité maximale tomshardware.com. Chaque module MI350X adopte le format OAM et est conçu pour une intégration dense en centre de données, avec une option de refroidissement liquide extrême sur le haut de gamme MI355X (qui a une puissance totale de carte allant jusqu’à 1 400 W pour des performances maximales) tomshardware.com tomshardware.com. Le MI350X refroidi par air fonctionne avec une enveloppe de puissance plus faible (~1 000 W). Les deux variantes partagent la même conception de base et sont compatibles avec les broches des systèmes « Universal Base Board » de la série MI300 existants, ce qui facilite les mises à niveau amd.com.

Performances et benchmarks : AMD affirme que la série Instinct MI350 représente un saut générationnel, en particulier pour l’inférence IA. Selon les chiffres d’AMD, la série MI350 offre une performance de calcul IA 4× supérieure et jusqu’à 35× plus de débit d’inférence IA par rapport à la génération précédente MI300 (CDNA 3) tomshardware.com tomshardware.com. Dans les benchmarks internes d’AMD, un seul MI350X surpasserait le modèle phare actuel de NVIDIA sur des indicateurs clés. Par exemple, lors de l’événement “Advancing AI 2025” d’AMD, la société a affirmé que les GPU de la classe MI350 atteignent jusqu’à 1,3× la performance d’inférence des offres de NVIDIA dans des tests équivalents, et devancent même d’environ 13 % sur certaines charges d’entraînement tomshardware.com tomshardware.com. Quelques comparaisons spécifiques sont apparues via des rapports industriels : une analyse d’HSBC citée par les médias a noté que le MI355X surpasse le B200 de NVIDIA sur certaines tâches d’inférence de grands modèles – environ 20 % plus rapide sur une charge DeepSeek R1 FP4, et 30 % plus rapide sur un test Llama 3.1-405B LLM (égale la performance du système massif GB200 de NVIDIA) smbom.com smbom.com. Ce sont des affirmations audacieuses qui suggèrent qu’AMD est compétitif à la pointe de l’inférence LLM. Les spécifications brutes de Tom’s Hardware l’expliquent : un seul MI355X peut atteindre 10 PFLOPS de calcul matriciel en FP4/FP6 (ou 20 PFLOPS avec la sparsité activée), tandis que le MI350X plafonne à environ ~5 PFLOPS FP16 et ~10 PFLOPS FP8 tomshardware.com tomshardware.com. En comparaison avec NVIDIA, AMD indique que le MI355X offre environ 2× le débit maximal FP64/FP32 du Blackwell (puisque NVIDIA les a réduits) tomshardware.com. À des précisions plus faibles comme FP16/FP8/FP4, le débit par GPU d’AMD est similaire à celui de Blackwell – le MI350X semble « égaler ou légèrement dépasser les équivalents Nvidia » dans la plupart des cas tomshardware.com tomshardware.com. Un point remarquable est le format FP6 : l’architecture d’AMD peut exécuter le FP6 au même rythme que le FP4, ce qu’ils présentent comme un élément différenciateur pour certains modèles tomshardware.com. En ce qui concerne les charges de travail limitées par la mémoire, l’énorme pool HBM3e du MI355X pourrait briller : AMD affirme que son accélérateur de 288 Go peut générer 40% de tokens LLM en plus par dollar que le B200 de NVIDIA, en partie grâce à la gestion de fenêtres de contexte ou de tailles de lot plus grandes sans débordement smbom.com smbom.com. Il faudra attendre des résultats MLPerf indépendants pour une confirmation complète – fin 2024, le matériel MI350 commence tout juste à être déployé – mais les premiers signes indiquent qu’AMD est bel et bien dans la course pour l’entraînement et l’inférence IA à grande échelle. Notamment, les accélérateurs de la série MI350 sont au cœur du futur supercalculateur exascale El Capitan et d’autres systèmes HPC, donc leurs performances FP64 et en précision mixte seront également testées dans des applications scientifiques. (AMD a traditionnellement dominé les performances GPU en FP64 ; par exemple, le précédent MI250X offrait ~47,9 TFLOPS FP64, bien au-dessus des 9,7 TFLOPS du NVIDIA A100, et la série MI300 a poursuivi cette tendance). Avec le MI350, AMD équilibre cette force HPC avec d’énormes gains de performance en IA.

Efficacité énergétique : Grâce au procédé avancé en 3 nm et aux améliorations architecturales, la série MI350 devrait être extrêmement économe en énergie pour le traitement de l’IA – bien que les niveaux de puissance absolus restent élevés. AMD annonce une amélioration de 35× des performances d’inférence par watt par rapport à la génération précédente, ce qui est en partie dû à l’utilisation des formats de données INT4/FP4 qui réalisent simplement plus d’opérations par joule amd.com amd.com. La MI350X offre bien plus de performances par carte que ses prédécesseurs, ce qui devrait se traduire par une meilleure efficacité au niveau du rack. Cependant, la consommation électrique du modèle phare MI355X, à 1,4 kW, est presque le double de celle de la MI300X (750 W) tomshardware.com. L’argument d’AMD est que cette enveloppe de puissance plus élevée s’amortit d’elle-même grâce à la densité : une MI355X offre tellement de performances qu’il faut moins de GPU au total, ce qui améliore finalement la performance par TCO (coût total de possession) au niveau du centre de données tomshardware.com tomshardware.com. En d’autres termes, il est possible de déployer un rack de nœuds MI355X au lieu de deux racks d’accélérateurs moins puissants, ce qui permet d’économiser sur le refroidissement, le réseau et les coûts d’infrastructure pour un même travail effectué. AMD met également en avant les gains d’efficacité de son architecture CDNA4 : le passage au 3 nm, l’utilisation de l’assemblage avancé et l’introduction de nouvelles instructions pour l’IA ont considérablement augmenté les performances par watt. Par exemple, la MI350 adopte de nouveaux formats de faible précision (FP4/FP6) qui réduisent considérablement les besoins en bande passante mémoire et en stockage pour un modèle donné, réduisant ainsi directement la consommation par inférence. Les solutions de refroidissement (liquide pour la MI355X) garantissent que les GPU peuvent maintenir des fréquences élevées sans limitation thermique. Tout cela suggère qu’AMD a conçu la MI350 non seulement pour rivaliser en vitesse brute, mais aussi en débit par dollar et par watt. Les commentaires des dirigeants vont dans ce sens : « Nous sommes infatigables dans notre rythme d’innovation, offrant les capacités de pointe et les performances attendues par l’industrie de l’IA, pour conduire la prochaine évolution de l’entraînement et de l’inférence IA en centre de données », a déclaré Brad McCredie, vice-président Accelerated Compute chez AMD, soulignant l’accent mis sur la valeur et la performance tomshardware.com.

Écosystème logiciel et cas d’utilisation : Historiquement, le logiciel a été le principal défi d’AMD dans le domaine de l’IA, mais l’entreprise a réalisé des progrès significatifs avec sa pile logicielle ouverte ROCm. Lorsque le MI350 sera largement lancé (prévu pour 2025), la plateforme et les bibliothèques ROCm 6+ d’AMD seront très matures, avec une prise en charge des principaux frameworks (PyTorch, TensorFlow, JAX) et bibliothèques de modèles. En fait, AMD s’est associé à des entreprises comme Hugging Face pour tester de manière proactive des centaines de milliers de modèles d’IA populaires sur le matériel de la série MI300, afin de garantir leur fonctionnement immédiat sur les GPU AMD amd.com amd.com. Ce type d’activation logicielle est crucial pour la confiance des clients. AMD a également intégré la prise en charge des optimisations de transformeurs populaires – par exemple, des logiciels pour exploiter le FP8/FP4, et des outils pour faciliter le portage du code CUDA vers HIP (l’API de programmation parallèle d’AMD). Bien que NVIDIA reste en tête en matière de finition logicielle, AMD positionne le MI350 comme une alternative viable pour les fournisseurs de cloud et les grandes entreprises souhaitant diversifier leur matériel d’IA. Notamment, Microsoft Azure, Meta (Facebook), et les principaux OEM (Dell, HPE, Lenovo) travaillent déjà avec les accélérateurs MI300X tomshardware.com tomshardware.com, et ils sont des candidats probables pour adopter le MI350 à partir de 2025. Par exemple, Azure propose des instances IA avec MI300A/X pour les services OpenAI, et Meta a validé le MI300 pour ses charges de travail internes tomshardware.com. Cette dynamique devrait se poursuivre avec la génération CDNA4. AMD explore également le partitionnement et le passage à l’échelle multi-GPU similaire au NVSwitch de NVIDIA – les cartes MI350 utilisent le même facteur de forme UBB qui prend en charge les liens Infinity Fabric d’AMD entre les GPU. Bien que les détails soient rares, des fuites suggèrent qu’AMD pourrait permettre de grandes configurations (par exemple, Instinct MI450X avec tissu IF128 connectant de nombreux GPU en 2026) tomshardware.com tomshardware.com. Pour l’instant, le MI350X peut être utilisé dans des configurations GPU 2P ou 4P avec des liaisons à haute vitesse. Les principaux cas d’utilisation du MI350 couvriront à la fois l’IA et le HPC : l’entraînement de grands LLM, le déploiement de iL’inférence pour des modèles comme ChatGPT ou des générateurs d’images, et l’accélération des simulations scientifiques (modélisation climatique, physique, etc.) qui mêlent de plus en plus l’IA au calcul traditionnel. Avec sa puissance FP64 et sa mémoire énorme, le MI350 peut gérer des simulations HPC ou de grandes analyses de graphes nécessitant une grande précision et beaucoup de mémoire, tout en assurant également l’entraînement de réseaux neuronaux sur le même système. Cette flexibilité, si elle est au rendez-vous, pourrait rendre la solution d’AMD attrayante aussi bien pour les laboratoires nationaux que pour les géants du cloud. Côté prix, AMD a été agressif : des rapports indiquent qu’AMD avait initialement fixé le prix du MI350X autour de 15 000 $, mais, face à la forte demande, l’a augmenté à environ 25 000 $ – ce qui reste un peu moins cher que l’équivalent de NVIDIA, qui se situe dans la fourchette de 30 à 40 000 $ smbom.com smbom.com. Les analystes y voient un signe de la confiance d’AMD dans la valeur du MI350 par rapport au Blackwell de NVIDIA. Comme l’a noté un média technologique, « AMD estime que les performances du MI350 peuvent rivaliser avec celles du Nvidia Blackwell B200, et malgré la hausse de prix, le MI350 reste plus abordable que l’offre de Nvidia. » smbom.com smbom.com.

Google TPU v6e « Trillium » – Architecture et performances

Aperçu de l’architecture : Le TPU v6e de Google, nom de code Trillium, est la sixième génération de l’unité de traitement tensoriel propriétaire de Google – un ASIC accélérateur d’IA conçu spécifiquement pour l’entraînement et l’inférence des réseaux neuronaux. Annoncé lors de Google I/O 2024, les TPUs Trillium sont conçus pour maximiser la performance par dollar sur les charges de travail ciblées par Google (grands transformeurs, modèles de recommandation, etc.) dans Google Cloud. Sur le plan architectural, une puce TPU v6e est très différente d’un GPU : elle contient un unique TensorCore qui abrite deux unités de multiplication matricielle (MXU) ainsi que des unités vectorielles et scalaires cloud.google.com cloud.google.com. Ces MXU implémentent d’immenses réseaux systoliques pour le calcul matriciel, adaptés aux calculs BF16 (bfloat16) et INT8 (historiquement, les TPU ne prennent pas en charge nativement l’arithmétique FP32/FP64 afin d’économiser du silicium). Avec Trillium, Google a considérablement augmenté la taille du cœur : les MXU du v6e sont plus grands et fonctionnent à des fréquences plus élevées que dans les TPUs précédents cloud.google.com. Le résultat est une augmentation de 4,7× du calcul maximal par puce par rapport à la dernière génération Cloud TPU v5e cloud.google.com cloud.google.com. Concrètement, une seule puce TPU v6e délivre 918 TFLOPS de BF16 en crête (contre ~197 TF sur le v5e) et environ 1,836 POPS (PetaOPS) d’INT8 de débit cloud.google.com cloud.google.com. Chaque puce est équipée de 32 Go de mémoire à large bande passante (HBM2e/HBM3) – soit le double des 16 Go du v5e cloud.google.com cloud.google.com. La bande passante mémoire par puce a également doublé pour atteindre 1,6 To/s cloud.google.com cloud.google.com. Bien que 32 Go par puce puisse sembler faible comparé à la mémoire GPU, les TPU sont conçus pour être utilisés en essaims, et Google a également doublé la bande passante de l’Inter-Chip Interconnect (ICI) (de 1 600 Gbps à 3 200 Gbps par puce) cloud.google.com cloud.google.com. Chaque puce v6e possède 4 liens ICI formant une topologie en tore 2D avec jusqu’à 256 puces dans un pod TPU cloud.google.com cloud.google.com. En essence, la philosophie de conception de Google est d’utiliser de nombreuses puces de taille modérée travaillant de concert, plutôt qu’une seule puce énorme. Un pod Cloud TPU v6e standard se compose de 256 puces (réparties sur 32 machines hôtes avec 8 puces chacune), toutes étroitement interconnectées pour l’entraînement collectif de très grands modèles cloud.google.com cloud.google.com. Google a également introduit le SparseCore de 3e génération dans Trillium – un coprocesseur spécialisé sur chaque puce dédié à l’accélération des charges de travail d’embedding et de recommandation volumineuses (en gérant plus efficacement les recherches de données clairsemées) cloud.google.com cloud.google.com. Cela répond à des cas d’usage comme le classement, les embeddings pour la recherche/les publicités, etc., qui sont essentiels pour l’activité de Google. Il est à noter que les TPU fonctionnent traditionnellement avec une précision numérique plus faible ; la v6e prend en charge bfloat16 et INT8, et il y a des indices qu’elle pourrait prendre en charge des formats float expérimentaux 8 bits ou 4 bits, bien que Google n’ait pas officiellement détaillé cela nextplatform.com nextplatform.com. (The Next Platform a émis l’hypothèse que FP8/FP4 pourraient être ajoutés à Trillium pour suivre les tendances de l’industrie nextplatform.com.) Le nœud de gravure et la consommation pour le TPU v6e n’ont pas été rendus publics, mais compte tenu des gains d’efficacité, il utilise probablement un procédé 5nm ou 4nm. Chaque puce pourrait consommer environ ~200–250 W (les puces TPU v4 précédentes étaient à ~175 W), mais les chiffres exacts ne sont pas divulgués. Google a mis en avant une efficacité énergétique supérieure de 67 % sur la v6e par rapport à la v5e cloud.google.com <a href="https://cloud.google.cocloud.google.com, indiquant une performance par watt bien supérieure.

Performance et évolutivité : Une seule puce TPU v6e offre environ 0,918 PFLOPS (918 TF) en BF16 et peut être massivement regroupée, donc les performances sont généralement discutées à l’échelle du pod. Un pod complet (256 puces) a un pic théorique de ~234,9 PFLOPS BF16 agrégé et plus de 1 exaOP/s en INT8 cloud.google.com cloud.google.com. En pratique, Google a démontré des performances impressionnantes en conditions réelles avec Trillium. Des modèles internes de Google tels que Gemini 1.5 (modèle de fondation nouvelle génération) et Imagen 3 (générateur d’images) ont été entraînés sur du matériel TPU v6 cloud.google.com. Google affirme que ces TPU permettent d’entraîner « la prochaine vague de modèles de fondation plus rapidement et de les servir avec une latence et un coût réduits » cloud.google.com cloud.google.com. Par exemple, dans un cas public, Google a noté que le passage du TPU v5e au v6e a permis un accélération de 4,7× sur une charge de travail basée sur un transformeur au niveau de la puce cloud.google.com. Un autre indicateur clé est la performance par TCO – Google indique que le v5e est à 0,65× et le v6e à 1,0 (référence) en performance/TCO, ce qui implique que le v6e offre ~54% de débit en plus par dollar que le v5e dans leurs déploiements cloud cloud.google.com cloud.google.com. Le doublement de la mémoire et de la bande passante de communication signifie que le v6e peut gérer des modèles beaucoup plus grands efficacement. Avec 32 Go par puce (et 8 puces par hôte), chaque hôte TPU dispose de 256 Go HBM au total, et un pod complet de 256 puces dispose de 8 To de HBM répartis sur le maillage – permettant effectivement l’entraînement de modèles avec des dizaines de milliards de paramètres en mode data-parallel ou model-parallel. En termes de benchmarks, Google ne soumet généralement pas ses TPUs à MLPerf, mais il existe des comparaisons anecdotiques. Le TPU v4 était à peu près comparable au NVIDIA A100 sur certaines tâches (du moins à l’échelle des pods), et le TPU v5e était une version optimisée pour le coût du TPU v5. Le v6e « Trillium » semble combler une grande partie de l’écart avec les Hopper/Blackwell de NVIDIA en calcul brut : par exemple, 918 TF BF16 est du même ordre de grandeur qu’un NVIDIA H100 (~1 000 TF FP16), bien qu’un seul Blackwell B200 à ~4 500 TF16 soit bien supérieur. Cependant, Google peut déployer 256 de ces puces (ou même des clusters multi-pods plus grands avec des interconnexions optiques cloud.google.com), atteignant des performances qui rivalisent avec les superordinateurs. Google indique également que TPU v6e est 67 % plus économe en énergie que v5e pour le même travail cloud.google.com, une statistique cruciale pour réduire les coûts du cloud. Concrètement, cela signifie que des tâches comme le service d’un grand modèle de langage peuvent être effectuées avec une consommation d’énergie bien moindre, ce qui se traduit par des économies pour Google et ses clients Cloud TPU. Le SparseCore de troisième génération de Trillium augmente considérablement le débit sur les systèmes de recommandation – un domaine où les GPU rencontrent souvent des difficultés en raison des opérations clairsemées limitées par la mémoire. En déléguant les recherches d’embeddings à SparseCore, Google annonce de grands gains pour des modèles comme le classement publicitaire cloud.google.com cloud.google.com. Globalement, les performances du TPU v6e sont ultra-optimisées pour les modèles de transformeurs, les CNN et les embeddings. Il ne prend probablement pas en charge le FP32/FP64, il ne serait donc pas utilisé pour des tâches HPC générales, mais pour l’entraînement IA à grande échelle, il fait partie des meilleurs – Google l’a qualifié de « notre TPU le plus performant et le plus économe en énergie à ce jour » cloud.google.com.

Efficacité et Déploiement : La stratégie de Google avec les TPU est de maximiser le débit par dollar dans le cloud. Le TPU Trillium en est l’exemple, offrant un meilleur rapport qualité/prix que les TPU précédents et, selon Google, une alternative compétitive à la location de GPU NVIDIA. Une analyse a noté que Google pourrait fixer le prix des instances TPU v6e à un peu plus de 2× le coût des v5e, mais comme elles sont 4 à 5× plus rapides, le coût net par unité de travail s’améliore tout de même de plus de 2× nextplatform.com. En effet, Google présente le v6e comme le « produit à la plus grande valeur » pour un large éventail de tâches d’IA (transformers, texte-vers-image, CNN pour la vision) dans les offres Cloud TPU cloud.google.com cloud.google.com. Les pods TPU v6e peuvent également s’étendre au-delà d’un seul pod : Google a introduit la technologie multislice et les Titanium IPUs pour connecter plusieurs pods de 256 puces via son réseau de datacenters cloud.google.com cloud.google.com. Cela pourrait permettre à des milliers de puces TPU v6e de travailler ensemble dans un « superordinateur à l’échelle d’un bâtiment », une extensibilité pratiquement illimitée pour des modèles ultra-larges – un concept que Google a évoqué pour l’infrastructure IA du futur cloud.google.com. En termes de disponibilité, Cloud TPU v6e est disponible (fin 2024) dans les régions Google Cloud via des instances comme ct6e-standard types de VM cloud.google.com. Les développeurs peuvent accéder à des configurations allant d’une seule puce (v6e-1) jusqu’à un pod complet (v6e-256), voire multi-pod via des accords spéciaux cloud.google.com cloud.google.com. Google propose des intégrations pour TensorFlow et JAX afin d’utiliser les TPU de manière transparente, et PyTorch est pris en charge via le compilateur XLA (de nombreux modèles PyTorch peuvent fonctionner sur TPU avec peu de modifications de code grâce à PyTorch XLA). Des frameworks de déploiement de modèles courants comme vLLM ont également été démontrés sur TPU v6e medium.com. L’écosystème TPU est plus fermé que CUDA/ROCm ; il n’est pas possible d’acheter un TPU et de l’exécuter sur site (en dehors de rares partenariats), donc les utilisateurs sont essentiellement ceux sur Google Cloud ou les équipes internes de Google. Cependant, les TPU de Google ont prouvé leur efficacité en alimentant presque toute laLes propres avancées de Google en matière d’IA – depuis la recherche sur les Transformers jusqu’aux modèles phares comme PaLM et Gemini – sont désormais proposées à des clients externes qui ont besoin d’une échelle massive sans acheter de GPU physiques. Une citation clé d’Amin Vahdat, vice-président/directeur général des Systèmes et de l’IA chez Google, résume ce lancement : « Nous sommes ravis d’annoncer Trillium, notre TPU de sixième génération, le plus performant et le plus économe en énergie à ce jour. » cloud.google.com Cela souligne l’intention de Google de continuer à repousser les limites des puces spécialisées pour l’IA afin de rivaliser avec les fabricants de GPU généralistes.

Comparaison des performances réelles et de l’efficacité énergétique

Chacun de ces accélérateurs excelle selon des critères différents, donc leur comparaison nécessite du contexte. Les NVIDIA B200 et AMD MI350 sont plus directement comparables (tous deux sont des GPU polyvalents pour l’IA/HPC), tandis que le TPU de Google est un ASIC cloud spécialisé uniquement pour l’IA. Il reste néanmoins instructif de voir comment ils se positionnent sur les tâches qu’ils visent tous – à savoir l’entraînement et l’inférence de grands modèles d’IA.

- Performance d’entraînement IA (BF16/FP16) : Sur le papier, un seul NVIDIA B200 offre le débit maximal le plus élevé (4,5 PFLOPS FP16) exxactcorp.com, soit à peu près l’équivalent de deux GPU MI350X ou de cinq puces TPU v6e (chacune à 0,918 PFLOPS BF16) cloud.google.com. En pratique, l’évolutivité multi-GPU et la maturité logicielle jouent un rôle important. NVIDIA a démontré qu’un cluster de GPU Blackwell (GB200 NVL) pouvait entraîner un LLM géant à une vitesse record – par GPU, environ 3× plus rapide que la génération précédente H200 developer.nvidia.com developer.nvidia.com. AMD, de son côté, revendique une vitesse d’entraînement ~1,13× supérieure à celle de NVIDIA dans certains tests tomshardware.com, mais cela fait probablement référence à des scénarios où la mémoire supplémentaire du MI355X ou le FP32/FP64 pourraient aider à la convergence. Le TPU v6e de Google peut entraîner efficacement des modèles comme PaLM lorsqu’il est déployé en pods, mais la performance d’une seule puce reste inférieure à celle des GPU. Par exemple, un serveur B200 à 8 GPU (DGX B200) peut surpasser un hôte TPU à 8 puces de façon significative pour l’entraînement, étant donné les 72 PFLOPS FP8 du DGX contre environ 7,3 PFLOPS BF16 pour l’hôte TPU nvidia.com cloud.google.com. Cependant, Google peut déployer 32 de ces hôtes (256 puces) pour forcer les gros travaux. En résumé, pour la vitesse brute d’entraînement sur un serveur, le B200 est probablement en tête, suivi du MI350 (qui devrait être dans la même fourchette), le TPU v6e n’atteignant son efficacité maximale qu’à l’échelle du pod.

- Inférence IA et Débit en Basse Précision : C’est sur ce point que les trois ont fait de grandes annonces. NVIDIA annonce jusqu’à 15× de gain de performance en inférence par rapport au H100 nvidia.com, grâce principalement au FP4. AMD met en avant un gain de 35× en inférence par rapport au MI300 et affirme que le MI355X dépasse le B200 de 20 à 30 % sur certaines tâches d’inférence LLM smbom.com. Le TPU v6e de Google, avec prise en charge de l’INT8 et potentiellement du FP8, est très optimisé pour l’inférence (67 % de performance par watt en plus qu’avant, principalement pour le service). À noter, le Blackwell de NVIDIA a l’avantage de la flexibilité : il peut exécuter n’importe quel modèle avec les frameworks GPU existants. Le MI350 d’AMD pourra exploiter les nouveaux FP4/FP8 dans PyTorch/TensorFlow dès qu’ils seront pris en charge, et AMD revendique un avantage de 40 % sur le coût par token pour le MI355X par rapport au B200 en inférence smbom.com. Le TPU de Google pourrait l’emporter sur la latence absolue à grande échelle – les TPU disposent d’interconnexions et de traitements par lots spécialisés pour servir de nombreuses requêtes (Google les utilise pour servir la Recherche et des services de type Bard à l’échelle mondiale). Si l’on prend en compte le coût, un pod TPU v6e offre probablement l’inférence à un coût inférieur à celui d’un cluster GPU équivalent pour certaines charges de travail, ce qui est l’argument de vente de Google. Par exemple, un blog de Google Cloud a noté une performance-prix 2,3× meilleure en passant de solutions GPU à TPU dans certains cas nextplatform.com. Tout dépend vraiment de la charge de travail ; les transformers avec beaucoup de calculs matriciels favorisent NVIDIA/AMD, tandis que les tâches de recommandation et à forte sparsité favorisent les atouts de SparseCore de Google.

- Mémoire et taille du modèle : AMD est clairement en tête en termes de mémoire brute par accélérateur : 288 Go HBM3e sur le MI355X tomshardware.com. Le B200 de NVIDIA dispose de 180 Go nvidia.com. Le TPU v6e de Google possède 32 Go par puce, mais effectivement 256 Go par hôte de 8 puces et 8 To sur un pod cloud.google.com. Pour les tâches à instance unique (un modèle tenant dans un seul accélérateur), AMD peut gérer les plus grands modèles (par exemple, un modèle nécessitant 250 Go de poids pourrait tenir sur un seul MI355X, alors qu’il faudrait le répartir sur deux B200 ou 8 puces TPU). Cela dit, NVIDIA et Google utilisent tous deux le parallélisme de modèle pour répartir les grands modèles sur plusieurs GPU/TPU. Le NVLink et le NVSwitch de NVIDIA permettent à plusieurs B200 d’agir comme un grand pool de mémoire (8×180 Go = 1,44 To dans un DGX, ce qu’ils ont utilisé pour faire tourner des modèles de plus de 400 milliards de paramètres dans MLPerf) nvidia.com developer.nvidia.com. Le pod TPU de Google regroupe de même un total de 8 To HBM. Ainsi, pour les modèles ultra-larges (centaines de milliards de paramètres), tous peuvent s’adapter via l’entraînement distribué – mais AMD pourrait permettre de faire tourner des modèles assez grands sans distribution (un modèle de programmation plus simple). De plus, la bande passante mémoire d’AMD est équivalente à celle de NVIDIA : 8 To/s contre 8 To/s tomshardware.com tomshardware.com, toutes deux bien supérieures aux 1,6 To/s par puce du TPU (même si le TPU compense avec plus de puces alimentant le modèle). Pour les modèles limités par la bande passante mémoire (comme les CNN de vision ou le ML parcimonieux), les GPU ont l’avantage en bande passante brute par appareil.

- Efficacité énergétique : Les trois fournisseurs ont amélioré les performances par watt, mais comment se comparent-ils ? NVIDIA n’a pas donné de chiffre simple de perf/W, mais la performance par watt pour l’IA de Blackwell a probablement doublé par rapport à Hopper (qui était dans la gamme ~TOPS/W). AMD indique explicitement 4× plus de calculs pour une puissance similaire en passant de CDNA3 à CDNA4, plus les gains de l’empilement 3D ; la densité de performance du MI350X (PFLOPS par watt) semble très élevée, bien qu’à une puissance absolue élevée. Le gain de 67 % en efficacité énergétique de Google est énorme – le TPU v6e effectue près de 5× plus de travail pour peut-être ~3× la puissance du v5e, soit une amélioration nette d’environ 1,67× en perf/W. Il est difficile de classer sans métriques identiques, mais pour le débit d’inférence par watt, Blackwell utilisant le FP4 prend probablement la couronne (puisque le FP4 double le débit avec un faible coût énergétique). Le FP4 d’AMD est similaire et ils revendiquent spécifiquement MI355X 20 PFLOPS avec sparsité à 1,4 kW smbom.com, soit ~14,3 TFLOPS par watt pour le FP4 sparse. Le B200 de NVIDIA à ~1,5 kW atteint 18 PFLOPS FP4 (sans besoin de sparsité) exxactcorp.com exxactcorp.com, soit environ 12 TFLOPS/W – légèrement inférieur si l’on compare ces chiffres directement. Avec la sparsité, Blackwell doublerait aussi, donc il pourrait atteindre ~24–30 TFLOPS/W dans les cas idéaux. En résumé, tous sont extrêmement efficaces énergétiquement pour l’IA par rapport à la génération précédente, et les différences peuvent se situer dans une fourchette de 10 à 20 %. L’efficacité réelle dépend aussi de l’utilisation (les TPU de Google excellent à forte utilisation dans les datacenters cloud, tandis que les GPU auto-hébergés peuvent parfois être inactifs).

Support logiciel et écosystème

Les trois plateformes disposent chacune d’écosystèmes logiciels distincts, qui peuvent être aussi importants que les capacités matérielles :

- NVIDIA (CUDA + AI Enterprise) : La pile de NVIDIA est la plus établie. Les développeurs utilisent CUDA et des bibliothèques comme cuDNN, TensorRT, NCCL, et d’autres qui ont été hautement optimisées pendant plus d’une décennie. Des frameworks tels que PyTorch et TensorFlow disposent d’un support natif de CUDA, ce qui signifie que les modèles s’exécutent sur les GPU NVIDIA avec un minimum d’efforts. Avec Blackwell, NVIDIA propose également des mises à jour comme le package TensorRT-LLM pour les grands modèles de langage et l’intégration Transformer Engine qui automatise la précision mixte (incluant désormais FP4) developer.nvidia.com. De plus, la suite logicielle AI Enterprise de NVIDIA (incluse avec les systèmes DGX) garantit la stabilité et le support pour les workflows d’IA en entreprise, et des outils comme NeMo Megatron simplifient l’entraînement de modèles massifs sur des clusters DGX nvidia.com. L’avantage de l’écosystème est évident : de nombreux chercheurs et ingénieurs en IA « pensent en CUDA » et bénéficient d’un vaste support communautaire et d’une documentation abondante pour les GPU NVIDIA. Les GPU Blackwell peuvent en grande partie réutiliser les logiciels optimisés pour Hopper ; NVIDIA a publié un kit d’outils CUDA optimisé pour Blackwell en même temps que la disponibilité du matériel. Cette compatibilité ascendante et descendante est un atout majeur – le code qui tournait sur V100/A100/H100 peut généralement être recompilé, voire parfois s’exécuter tel quel sur B200 (simplement plus rapidement). Les partenariats étroits de NVIDIA avec les éditeurs de logiciels et les plateformes cloud signifient également que même les logiciels d’IA propriétaires ou fermés (par exemple, certaines plateformes d’IA d’entreprise) privilégient souvent d’abord la prise en charge NVIDIA.

- AMD (ROCm + HIP) : ROCm (Radeon Open Compute) d’AMD est une pile logicielle open source pour le calcul GPU qui a beaucoup mûri ces dernières années. Pour les MI300/MI350, AMD propose ROCm 6 qui prend en charge tous les principaux frameworks d’IA via des backends natifs ou HIP (Heterogeneous-compute Interface for Portability). HIP est l’API d’AMD interopérable avec CUDA – elle permet de compiler de nombreux codes CUDA pour les GPU AMD avec peu de modifications. AMD a collaboré avec PyTorch pour développer PyTorch Direct ML for ROCm, et avec les équipes de TensorFlow et JAX pour activer ces frameworks sur ROCm également amd.com. En 2024, PyTorch sur ROCm pouvait exécuter des modèles de transformeurs populaires sur MI300X avec seulement de légères différences de performance par rapport à NVIDIA (à condition que le modèle n’utilise pas d’opérations spécifiques à NVIDIA). De plus, AMD optimise les noyaux de modèles populaires (attention, bloc de transformeur, convolution, etc.) pour les architectures CDNA. Un point fort : les tests nocturnes de Hugging Face sur 700 000 modèles sur MI300X garantissent que la diversité du hub de modèles est validée sur AMD amd.com, ce qui donne confiance que de nombreuses architectures (BERT, GPT, Stable Diffusion, etc.) fonctionneront sur MI350 dès le lancement. ROCm dispose encore d’une communauté d’utilisateurs plus restreinte que CUDA, et les outils/débogage sur AMD peuvent être plus difficiles en raison de sa relative nouveauté. Mais AMD répond à cela en collaborant avec des universités, des laboratoires nationaux et des fournisseurs de cloud pour constituer une base d’expertise autour des GPU Instinct. Ils mettent également l’accent sur les standards ouverts – par exemple, la prise en charge de PyTorch/XLA (également utilisé par les TPU) et l’offloading OpenMP pour le code HPC. L’écart logiciel se réduit ; si les modèles d’une organisation reposent sur des noyaux CUDA personnalisés, le portage vers AMD peut demander des efforts, mais pour de nombreux modèles courants, il devient de plus en plus possible de simplement « échanger et exécuter ». Le MI350 d’AMD utilisera également MIOpen (analogue à cuDNN) pour les routines d’apprentissage profond et les compilateurs AOMP pour le HPC. Un défi est qu’AMD évolue rapidement – MI250, MI300, MI350 présentent tous quelques différences – donc les logiciels doivent suivre les nouvelles fonctionnalités comme FP4/FP6. Mais étant donné que le MI350 utilise la même plateforme UBB et étend en grande partie le MI300, le support logiciel devrait être prêt (le MI350 a été mentionné comme étant utilisé comme « proxy » dans les projections lors des évaluations de performance du MI300X amd.com, ce qui implique que des prototypes logiciels étaient en test). En résumé, l’écosystème AMD n’est pas encore aussi plug-and-play que celui de NVIDIA, mais pour les utilisateurs engagés, il est viable et s’améliore rapidement, abaissant la barrière à l’adoption des GPU MI350, en particulier dans des environnements contrôlés comme les superordinateurs ou les instances cloud gérées.

- Google TPU (TensorFlow & JAX sur Cloud TPU) : L’écosystème du TPU v6e est assez différent car il n’est disponible qu’en tant que service. Les utilisateurs ne gèrent pas les pilotes ou les bibliothèques bas niveau ; ils accèdent aux TPU via l’API Cloud TPU de Google ou via les intégrations dans TensorFlow et JAX. Google fournit le compilateur TPU (XLA) qui transforme les graphes de calcul en code exécutable sur TPU. Pour TensorFlow, c’est presque transparent – vous pouvez distribuer un modèle sur TPU en utilisant des API de haut niveau (tf.distribute.TPUStrategy). Pour JAX (que Google privilégie pour la recherche), le compilateur jax.jit peut cibler efficacement les TPU, et de nombreux modèles de recherche Google sont écrits en JAX+Flax pour tourner sur TPU. Le support de PyTorch sur TPU a historiquement pris du retard, mais avec les TPU v5e et v6e, Google et Meta ont collaboré sur PyTorch XLA qui permet d’exécuter du code PyTorch sur TPU avec des modifications minimes. C’est crucial, car PyTorch est le framework dominant dans l’industrie. Il existe certaines limitations (toutes les opérations PyTorch ne sont pas compatibles TPU, et un réglage des performances est parfois nécessaire), mais de nombreux modèles courants peuvent être exécutés. De plus, les outils de Google comme les pipelines tf.data, le profileur TPU, et les tableaux de bord Cloud Monitoring sont disponibles pour aider à optimiser les pipelines d’entrée et à déboguer les problèmes de performance sur TPU cloud.google.com cloud.google.com. Un avantage de l’écosystème TPU est que vous bénéficiez d’une expérience managée – vous n’avez pas à vous soucier des versions logicielles ou des incompatibilités de pilotes ; Google garantit que toute la pile (du silicium au refroidissement) fonctionne immédiatement. L’inconvénient est une flexibilité moindre : vous ne pouvez pas, par exemple, écrire du code de noyau personnalisé pour TPU (sauf à écrire des opérations personnalisées dans le sous-ensemble compilable de TensorFlow). Si votre modèle utilise une opération non supportée par XLA, vous devez attendre que Google l’ajoute ou trouver une solution de contournement. De plus, certains types de modèles (comme ceux très dépendants du contrôle de flux dynamique) ne s’adaptent pas bien au paradigme des TPU, orienté batch et compilation statique. Mais pour l’essentiel du deep learning – les grandes multiplications de matrices – les TPU sont très efficaces. Google a également pré-construit des implémentations hautes performances pour des éléments comme l’attention multi-tête, les couches Transformer, etc., dans leurs bibliothèques TensorFlow et JAX pour TPU. Ils intègrent en continu leurs recherches (telles que des optimisations pour mixture-of-experts, des stratégies de sharding efficaces, etc.) dans le logiciel cloud TPU. Ainsi, si votre cas d’usage s’aligne avec celui de Google (LLM, modèles de vision, etc.), le logiciel TPU peut être très robuste. Une autre partie de l’écosystème TPU est constituée des services de plus haut niveau de Google : par exemple, Pathways (pour l’inférence multi-hôte) et des solutions managées comme Vertex AI peuvent exploiter les TPU en arrière-plan. Cela abstrait encore davantage le matériel pour l’utilisateur final, rendant les avantages du TPU accessibles sans effort d’ingénierie poussé. En somme, l’écosystème du TPU v6e est idéal pour ceux déjà dans l’univers Google Cloud et TensorFlow/JAX, mais il est moins accessible à ceux qui souhaitent une solution sur site ou un contrôle total (ce qui est voulu, car Google utilise les TPU pour attirer les utilisateurs vers sa plateforme cloud).

Scénarios de déploiement et disponibilité

NVIDIA, AMD et Google ont chacun des modèles de déploiement et des calendriers distincts pour ces accélérateurs :

- Disponibilité du NVIDIA Blackwell B200 : Les GPU Blackwell de NVIDIA ont été présentés autour du GTC 2024, et fin 2024, ils sont passés en production complète. Les appliances DGX B200 (8× GPU B200) sont désormais la pierre angulaire de l’offre de centres de données IA de NVIDIA, avec des livraisons aux clients clés et au cloud de NVIDIA lui-même (DGX Cloud) commençant vers le quatrième trimestre 2024 developer.nvidia.com. D’ici 2025, les principaux fournisseurs de cloud comme AWS, Azure, GCP et Oracle devraient proposer des instances B200, comme l’indique NVIDIA developer.nvidia.com. Les entreprises peuvent également acheter des cartes serveurs HGX B200 via des OEM comme Dell, HPE, Supermicro, etc. Le DGX B200 (avec 8 GPU, deux CPU Xeon, réseau, 1,44 To de HBM au total) est un système haut de gamme coûtant de l’ordre de 500 000 $+ (rumeur autour de 515 000 $) modal.com. Le prix par GPU se situe dans les dizaines de milliers ; selon les discussions du secteur, une seule carte B200 serait affichée à 30 000–40 000 $ selon le volume smbom.com. Les premiers utilisateurs incluent des laboratoires de recherche entraînant des modèles d’IA de pointe et des entreprises construisant des clusters IA privés – essentiellement ceux qui ont poussé le Hopper H100 à ses limites et ont besoin du prochain bond en avant. NVIDIA déploie également les GPU Blackwell dans ses superpuces : le Grace-Blackwell GB200 (1 CPU Grace + 2× B200 sur une carte, connectés par NVLink-C2C) est conçu pour les modèles géants qui bénéficient d’une intégration CPU-GPU étroite et d’une mémoire énorme (le CPU Grace ajoute 512 Go de mémoire LPDDR). Cette configuration GB200 « Ultra GPU » vise les charges de travail fusionnant HPC et IA et est prévue pour 2025, avec un prix annoncé autour de 60 000–70 000 $ par module nextplatform.com. En résumé, Blackwell sera omniprésent dans le haut de gamme de l’IA d’ici 2025 – toute organisation pouvant se le permettre et ayant besoin des meilleures performances pour l’entraînement ou l’inférence envisagera de déployer des B200, soit dans des clusters sur site (pour la souveraineté des données ou des besoins d’utilisation constante), soit via la location dans le cloud (pour une montée en charge occasionnelle). Le vaste réseau de partenaires de NVIDIA garantit que, des solutions SuperPOD jusqu’aux petits serveurs 4 GPU, les GPU Blackwell seront disponibles sous diverses formes.

- Disponibilité de l’AMD Instinct MI350 : AMD a indiqué que les accélérateurs MI350X et MI355X devraient être disponibles en 2025 amd.com amd.com. Le premier silicium a été présenté à la mi-2024, et à la mi-2025 AMD a indiqué avoir commencé à expédier des unités de production MI350X (en quantités limitées) tomshardware.com tomshardware.com. La montée en volume est prévue pour la fin 2025, à mesure que les déploiements majeurs seront mis en ligne. Un déploiement très attendu concerne le supercalculateur El Capitan du DOE américain (au Lawrence Livermore National Lab), qui utilisera une variante du MI300 – potentiellement mise à niveau vers le MI350 au moment de l’installation. De plus, des géants du cloud comme Microsoft se sont publiquement alignés avec AMD : Azure a annoncé son intention de proposer des VM de la série MI300, et on peut supposer que le MI350 suivra si les performances sont au rendez-vous tomshardware.com. Il y a également des rapports sur Meta évaluant le MI300/MI350 pour leur infrastructure IA, ce qui, si concluant, pourrait mener à de grosses commandes (Meta a historiquement surtout utilisé NVIDIA, mais la pression sur les coûts pourrait les pousser à intégrer AMD). Des ODM comme Lenovo et Supermicro ont présenté des systèmes prenant en charge les modules MI300 OAM, donc ceux-ci prendront également en charge le MI350. Cependant, au début, la disponibilité pourrait être limitée – AMD gagne du terrain mais doit encore renforcer ses chaînes d’approvisionnement et le support logiciel. Comme l’actualité sur la hausse des prix l’indique, la demande est suffisamment forte pour qu’AMD ait relevé le prix du MI350 d’environ 66 % à la mi-2025 smbom.com smbom.com, peut-être en raison de grosses précommandes. On pourrait voir des accélérateurs MI350 dans les offres cloud d’ici fin 2025 ou début 2026 ; un défi étant que les hyperscalers ont besoin de temps pour valider les logiciels et les performances à grande échelle. Le rythme annuel de la feuille de route d’AMD (Instinct MI400 attendu en 2026) <a href="https://www.amd.com/en/newsroom/press-releases/2024-6-2-amd-accelerates-pace-of-data-center-ai-innovation-.html#:~:text=The%20updated%20roadmap%20starts%20with,the%20AMD%20CDNA%20%E2%80%9CNext%E2%80%9D%20architecture" target="_blank" rel="noramd.com amd.com suggère que le MI350 sera le produit phare tout au long de 2025. En ce qui concerne les cas d’utilisation, les premiers clients seront probablement ceux qui ont besoin de la capacité mémoire (par exemple, l’entraînement de très grands modèles ou l’analyse de big data) ou ceux recherchant de meilleurs prix que NVIDIA. Les entreprises disposant déjà de code CUDA pourraient adopter AMD lentement, mais celles qui développent de nouvelles charges de travail (surtout sur PyTorch ou pour le service d’inférence) pourraient se lancer si le support ROCm est solide. L’écosystème OEM pour AMD Instinct est également en croissance : HPE, Dell et d’autres proposeront des modèles de serveurs avec MI350 pour les clients qui en feront la demande. AMD positionne le MI350 à la fois pour les méga-projets d’IA et le cloud grand public – attendez-vous à des annonces de déploiements de MI350 dans des superordinateurs, des plateformes d’IA cloud, et peut-être même dans certains systèmes IA clés en main d’OEM (similaires au DGX, mais à base d’AMD). Côté prix, comme indiqué, AMD propose des tarifs légèrement inférieurs à ceux de NVIDIA : peut-être environ 25 000 $ par GPU pour de grandes quantités smbom.com. Si ces prix se confirment, on pourrait voir un serveur 8xMI355X (avec environ 2,3 To de HBM au total) proposé à un prix inférieur à celui d’un NVIDIA DGX de taille similaire – une proposition de valeur tentante si les performances sont à la hauteur des attentes.

- Disponibilité de Google Cloud TPU v6e : Le TPU v6e (Trillium) a été annoncé en mai 2024 et rendu disponible peu de temps après sur Google Cloud (il a également été présenté lors de SC24 en novembre 2024) servethehome.com. Google introduit généralement la disponibilité des TPU région par région ; à la fin de 2024, les pods TPU v6e (256 puces) étaient probablement accessibles à certains clients Google Cloud sélectionnés (Google permet souvent à ses équipes de recherche et à certains partenaires d’utiliser les nouveaux TPU en premier, puis les ouvre plus largement). La documentation officielle montre la prise en charge des types d’instances TPU v6e de 1 puce jusqu’à 256 puces cloud.google.com, ce qui signifie qu’ils sont essentiellement utilisables publiquement maintenant. Tout utilisateur Google Cloud peut les demander via la console Cloud ou l’API (sous réserve d’approbation du quota, car ce sont des ressources coûteuses). Scénario de déploiement pour TPU v6e : il s’agit essentiellement des centres de données Google Cloud – contrairement aux GPU, vous ne pouvez pas déployer de TPU sur site. Ainsi, les utilisateurs ciblés sont ceux prêts à exécuter leur entraînement/inférence sur GCP. Notamment, Google a intégré le TPU v6e dans ses propres produits : par exemple, la recherche interne en IA de Google a probablement basculé sur v6e pour le développement de nouveaux modèles (Gemini, etc.), et des services comme Bard AI de Google ou la Recherche avec des fonctionnalités IA exploitent vraisemblablement des pods v6e pour servir les requêtes efficacement. Google propose également les TPU via son service géré Vertex AI pour une interface de plus haut niveau (ainsi, un client pourrait ne même pas savoir qu’il utilise un TPU, seulement que son modèle s’entraîne rapidement sur Vertex AI). Début 2025, le TPU v6e est l’une des offres les plus avancées du catalogue GCP, et Google élargira probablement la disponibilité à mesure que la demande augmentera. En termes de coût, Google n’a pas publié de tarification pour v6e au moment de la rédaction ; à titre de référence, les pods TPU v4 coûtaient des milliers de dollars par heure. On s’attend à ce que le TPU v6e soit proposé à un tarif premium mais reste compétitif par rapport à la location d’un nombre équivalent de GPU haut de gamme. La stratégie cloud TPU de Google a historiquement été d’être moins chère que le GPU pour l’entraînement (le TPU v3 était assez rentable par rapport au V100). Si cela se confirme, on pourrait voir le v6e proposé à un tarif offrant environ 50 % de meilleur $/unité d’entraînement qu’une VM basée sur H100. Une source communautaire a indiqué qu’un pod TPU v6e (256 puces) pourrait coûter de l’ordre de 1000 $+/heure, ce qui n’est viable que pour des projets bien financés mais peut être plus efficace que de gérer des dizaines de serveurs GPU pour une courte période. Globalement, le déploiement du TPU v6e est lié au succès de Google Cloud à attirer des charges de travail IA. Certaines entreprises (comme Midjourney pour la génération d’images, ou Character AI pour les chatbots) utiliseraient les TPU Google en backend – ces mises à niveau v6e leur profiteront directement. La contrainte est que ces solutions doivent être sur GCP ; les entreprises fortement investies dans AWS/Azure pourraient passer à côté des TPU pour des raisons logistiques. Mais pour celles ouvertes au multi-cloud ou déjà sur GCP, le v6e offre un outil puissant. Google continuera d’utiliser les TPU comme un moyen de différencier son cloud pour l’IA – en disant essentiellement, si vous voulez l’entraînement le plus rapide pour le coût le plus bas, venez sur GCP et utilisez les TPU au lieu de louer des GPU tiers. C’est une approche différente de NVIDIA et AMD, qui vendent du matériel directement ou via des OEM.

Perspectives de nouvelle génération et paysage concurrentiel

La bataille actuelle entre les Blackwell de NVIDIA, les séries Instinct MI300/350 d’AMD et les TPU de Google est intense, mais la feuille de route à venir laisse penser que la concurrence ne fera que s’intensifier. Chaque entreprise prévoit une prochaine génération qui s’appuiera sur les points forts (et tentera de corriger les faiblesses) de ces puces actuelles :- Prochaine génération de NVIDIA (après Blackwell) : NVIDIA a historiquement fonctionné sur un rythme de 2 ans pour ses principales architectures GPU. Après Blackwell (2024/2025), la prochaine architecture – nom non confirmé, mais probablement un autre nom de figure célèbre – est attendue vers 2026 ou 2027. Bien que les détails soient rares, quelques spéculations éclairées sont possibles. D’abord, NVIDIA poursuivra probablement sa stratégie de spécialisation des GPU pour l’IA. Avec Blackwell, ils ont déjà minimisé le FP64 ; à l’avenir, on pourrait voir une divergence encore plus marquée où NVIDIA proposerait des gammes ou des modes de produits séparés pour les « accélérateurs IA » et les « accélérateurs HPC ». En fait, certains rapports suggèrent que NVIDIA pourrait scinder ses GPU phares en gammes spécialisées pour l’IA vs. HPC selon les cas d’usage tomshardware.com. Cela pourrait signifier une variante avec une densité maximale de cœurs tensoriels et une autre avec plus de FP64/FP32 pour le calcul scientifique. On observe aussi la tendance des GPU à s’intégrer davantage avec les CPU : le CPU Grace de NVIDIA (basé sur Arm) fait désormais partie de leur plateforme, et les superpuces Grace+Blackwell « GB » annoncent un couplage plus étroit entre la mémoire CPU et la mémoire GPU. Il ne serait pas surprenant que la prochaine architecture introduise un package CPU/GPU unifié ou une cohérence mémoire CPU-GPU plus large (NVLink-C2C offre déjà la cohérence de cache entre Grace et le GPU). Une autre caractéristique probable est la poursuite de l’expansion de la mémoire et de l’interconnexion – la mémoire HBM4 ou HBMNext pourrait apparaître, poussant la bande passante mémoire vers 10+ To/s par GPU. NVIDIA pourrait aussi passer à un nœud de gravure plus petit (peut-être TSMC 3nm ou même 2nm si le calendrier est 2026/27), ce qui permettrait d’intégrer plus de transistors. Ceux-ci pourraient être utilisés pour augmenter le nombre de SM, la taille du cache, ou de nouvelles unités fonctionnelles. Une possibilité intrigante est l’ajout d’accélérateurs spécifiques à l’IA sur le GPU : par exemple, Blackwell a ajouté le Transformer Engine pour le FP8/FP4. Les futurs GPU pourraient intégrer du matériel dédié à des modèles comme la recommandation (un domaine ciblé par AMD et Google avec SparseCore, etc.). Jensen Huang a aussi évoqué des recherches à long terme sur les interconnexions optiques, les DPU et l’intégration de la photonique – peut-être pas pour la prochaine génération immédiate, mais à l’horizon pour continuer à faire évoluer le réseau. En termes de positionnement, NVIDIA cherchera à maintenir son leadership dans les solutions IA de bout en bout. Lorsque les MI400 ou MI500 d’AMD arriveront, NVIDIA répliquera avec sa prochaine architecture. La concurrence garantit probablement que la prochaine génération de NVIDIA sera nettement plus puissante (peut-être un nouveau bond de 2 à 3× en performance IA) pour garder son avance. Les prix pourraient aussi évoluer – si AMD continue de concurrencer sur les tarifs, NVIDIA pourrait proposer des options plus « souples » (sans jeu de mots avec Grace), peut-être via des partenariats cloud ou des offres groupées (ex : remises sur les crédits DGX Cloud). Un point à surveiller est la possible incursion de NVIDIA dans des puces spécifiques à un domaine : ils ont déjà des GPU et des DPU, mais créeront-ils un jour un ASIC matriciel dédié façon TPU ? Jusqu’ici, ils n’en ont pas eu besoin, mais si l’approche de Google venait à empiéter sur le marché de NVIDIA, ce dernier pourrait réagir en créant une variante de son GPU réduite aux seuls cœurs tensoriels et vendue comme accélérateur d’inférence. Pour l’instant, cependant, l’approche GPU leur offre une flexibilité qui leur réussit.

- Prochaine génération d’AMD (MI400 et au-delà) : AMD a partagé publiquement une feuille de route approximative : après CDNA4 (série MI350 en 2025), l’architecture CDNA “Next” alimentera la série Instinct MI400 attendue en 2026 amd.com amd.com. Fait intéressant, certaines premières informations suggèrent que la MI400 pourrait représenter un saut substantiel, intégrant peut-être même des technologies initialement prévues pour la MI500 nextplatform.com. Un rapport mis à jour a affirmé qu’un GPU MI400X pourrait être ~10× plus rapide que le MI300X et serait destiné à un nouveau système “Helios” à l’échelle rack avec des CPU EPYC “Venice” tomshardware.com. Cela laisse entendre qu’AMD travaille non seulement sur la puce mais aussi sur l’innovation au niveau du système (similaire à la stratégie Grace+GPU de NVIDIA). Il a également été question d’un Instinct MI450X avec IF128 (128 lignes Infinity Fabric) pour 2026 tomshardware.com, ce qui suggère une conception permettant de connecter 128 GPU dans un rack de façon transparente – analogue aux réseaux NVLink Switch de NVIDIA. Pour la MI400, on peut s’attendre à une transition vers un procédé encore plus récent (possiblement TSMC 2nm si le calendrier le permet, ou un 3nm amélioré), un packaging 3D plus avancé (peut-être même l’intégration de HBM au-dessus des dies de calcul, etc.), et probablement une augmentation supplémentaire de la capacité et de la bande passante mémoire. AMD intégrera probablement toute nouvelle technologie mémoire disponible (HBM4 ou HBM3e avec des densités encore plus élevées). Côté calcul, vu les progrès d’AMD, la MI400 pourrait introduire la prise en charge de types de données encore plus petits (FP2 ? Int4 complet ? à voir) et une utilisation plus agressive de la parcimonie et des instructions axées IA. Les récentes annonces d’AMD concernant de futurs produits IA (comme la mention de GPU “Radeon AI” pour le marché prosumer tomshardware.com) indiquent leur volonté de couvrir une plus grande part du marché. D’ici la MI400 ou MI500, AMD pourrait aussi unifier certaines fonctionnalités des GPU grand public (gaming) dans la gamme IA (par exemple, exploiter les cœurs graphiques RDNA pour certaines charges mixtes si besoin). En termes de positionnement, AMD vise clairement le leadership en performance par dollar. Si la MI350 gagne du terrain, la MI400 ira encore plus loin, pouvant dépasser NVIDIA sur certains indicateurs si possible. Par exemple, AMD pourrait choisir de largement surpasser NVIDIA en mémoire (imaginez une MI400 avec 512 Go de HBM) ou en support de précision arithmétique (AMD pourrait conserver un taux FP64 complet, intéressant les centres HPC, alors que NVIDIA a réduit ce support – ce qui permettrait à AMD de remporter des contrats HPC). AMD a également acquis Xilinx, donc une wilLa carte d, c’est la façon dont ils pourraient intégrer une FPGA ou une logique adaptative dans leurs accélérateurs. On pourrait imaginer de futures plateformes Instinct qui incluent certains cœurs reconfigurables pour des tâches spécialisées. En bref, la feuille de route d’AMD montre une cadence annuelle maintenant amd.com – ils ne sont plus une ou deux générations derrière NVIDIA ; ils sont au coude-à-coude. S’ils réussissent bien avec MI400 en 2026 et MI500 vers 2027 (comme certaines fuites le suggèrent, telles que « MI500X en 2027 » tomshardware.com tomshardware.com), AMD pourrait émerger comme un co-leader dans les accélérateurs IA, forçant un marché véritablement compétitif. C’est une bonne nouvelle pour les acheteurs, car cela tend à faire baisser les coûts et à stimuler l’innovation.

- La prochaine génération de Google (TPU v7 et plus) : Google n’a pas officiellement parlé d’une TPU v7, mais il est presque certain qu’ils y travaillent. Historiquement, Google a sorti une nouvelle génération de TPU environ tous les 1 à 1,5 ans (TPU v4 en 2020–21, v4i/v5e en 2022–23, v6 en 2024). Ainsi, une TPU v7 pourrait arriver en 2025 ou 2026. Un point intéressant est que Google propose souvent une “variante” : pour la v4, il y avait v4 et v4i (optimisée pour l’inférence), pour la v5 il y avait v5e (version moins chère, adaptée à l’extension). L’article de The Next Platform a émis l’hypothèse que la TPU v6 pourrait aussi avoir plus tard une puce orientée inférence “v6i” nextplatform.com. Si c’est le cas, Google pourrait introduire une TPU v6i avec peut-être moins de MXU mais plus de puces par pod ou autre chose pour maximiser le débit par dollar pour le service. Alternativement, la TPU v7 pourrait unifier les deux besoins. Techniquement, on pourrait voir Google intégrer la prise en charge de précisions encore plus faibles ; puisque d’autres ont du FP4, Google veillera probablement à ce que la TPU v7 prenne en charge FP8, FP4 (probablement en émulation logicielle dans le format bfloat16 ou via un nouveau matériel). Google pourrait aussi augmenter la mémoire – une limitation de longue date des TPU a été la mémoire relativement faible par puce, mais avec la v6 ils ont doublé à 32 Go. Si HBM3 et l’empilement 3D le permettent, la TPU v7 pourrait passer à 64 Go par puce, par exemple, ce qui aiderait pour les modèles plus grands et réduirait aussi le besoin de partitionner autant. Un autre domaine est l’interconnexion : Google utilise déjà des liaisons optiques pour le multi-pod, mais ils pourraient passer à un tore 3D ou d’autres topologies pour améliorer la latence des opérations collectives. On peut aussi s’attendre à plus d’intégration avec le réseau et l’infrastructure de Google : la mention des “Titanium IPUs” pour connecter les pods cloud.google.com suggère que Google pourrait intégrer des commutateurs réseau intelligents ou des interposeurs photoniques dans les futurs systèmes pour passer à une échelle encore plus grande (dizaines de milliers de puces). En termes de concurrence, le programme TPU de Google est tourné vers l’interne (pour soutenir les produits Google) mais aussi vers l’extérieur pour attirer les clients cloud. Ils continueront de positionner les TPU comme la solution la plus rentable pour entraîner d’énormes modèles – même si NVIDIA ou AMD ont des puces plus rapides, Google peut faire valoir que ses pods TPU, à grande échelle, offrent des résultats moins chers (puisque Google contrôle toute la pile et peut fixer des prix agressifs). Un défi pour Google est l’écart logiciel pour les utilisateurs externes – ils devront peut-être investir davantage dans des outils facilitant la migration du GPU vers le TPU. Sinon, beaucoup choisiront encore les GPU malgré le coût, simplement par habitude. Il ne serait pas surprenant que Google propose un jour des TPU à plus grande mémoire ou des systèmes hybrides (imaginez un TPU avec un CPU intégré ou plus de DRAM) pour les rendre plus polyvalents. Pour l’instant, cependant, Google gardera probablement les TPU focalisés : de purs calculateurs ML déployés par milliers dans ses centres de données. À mesure que la demande en IA générative augmente, Google fera évoluer les déploiements de TPU pour répondre à ses besoins (pour la recherche, Maps, les recommandations YouTube, etc.), ce qui signifie que la TPU v7 et les suivantes seront centrales pour l’avenir de l’IA chez Google. À noter également, d’autres hyperscalers pourraient réagir en développant leurs propres puces (Amazon a les ASICs Trainium et Inferentia, même s’ils ne sont pas encore aussi avancés ; Microsoft serait aussi en train de travailler sur une puce IA). Donc Google ne sera pas seul – mais les TPU v6e et v7 placent la barre très haut pour les nouveaux venus. Dans le paysage plus large, si les clients cloud se tournent de plus en plus vers les TPU pour des raisons de coût, cela pourrait pousser NVIDIA et AMD à ajuster leurs prix ou leurs stratégies cloud. Cependant, de nombreuses entreprises préféreront encore la flexibilité des GPNous, à moins que les TPU de Google ne deviennent beaucoup plus faciles à adopter sans verrouillage.

Résumé du paysage concurrentiel : En 2025, nous assistons à une compétition à trois où NVIDIA domine la part de marché et l’écosystème, AMD réduit agressivement l’écart avec une proposition de valeur matérielle convaincante, et Google exploite son approche verticalement intégrée pour déployer les capacités d’IA à grande échelle. Jensen Huang de NVIDIA souligne souvent que nous sommes dans une « nouvelle ère de l’informatique » portée par l’IA générative, et NVIDIA veut être pour cette ère ce qu’elle a été pour l’ère du PC et du jeu vidéo – la plateforme par défaut. Lisa Su, PDG d’AMD, met quant à elle l’accent sur le choix et l’ouverture, positionnant AMD Instinct comme offrant « des performances et une valeur exceptionnelles », pour citer le vice-président Brad McCredie, sur un marché qui a cruellement besoin de plus d’un fournisseur tomshardware.com. Les dirigeants de Google (comme Amin Vahdat) mettent en avant l’efficacité et la durabilité – le fait que les TPU peuvent effectuer plus de travail par watt, en accord avec les objectifs de coût et d’environnement cloud.google.com cloud.google.com. Au final, chaque entreprise joue sur ses points forts : NVIDIA avec une stratégie full-stack étroitement intégrée, AMD avec une approche disruptive en coût et riche en mémoire, et Google avec une solution sur mesure optimisée pour l’hyperscale. Pour les clients et l’industrie, la bonne nouvelle est que les performances du matériel IA explosent tandis que les logiciels gomment progressivement les différences. Il est concevable que les frameworks futurs permettent de cibler dynamiquement le matériel le plus adapté à une charge de travail donnée (par exemple, entraîner sur GPU, inférer sur TPU, etc.).

Conclusion : Les NVIDIA Blackwell B200, AMD Instinct MI350 et Google TPU v6e sont tous des merveilles d’ingénierie répondant à la demande insatiable de calcul pour l’IA. Le B200 de NVIDIA offre une vitesse fulgurante et un écosystème éprouvé, le MI350 d’AMD propose une mémoire énorme et des performances compétitives à un coût (potentiellement) inférieur, et le TPU v6e de Google délivre une efficacité et une échelle remarquables pour ceux qui utilisent son cloud. En avançant en 2025 et au-delà, nous verrons ces accélérateurs déployés partout, des superordinateurs relevant de grands défis scientifiques à l’IA en coulisses qui alimente les services internet utilisés par des milliards de personnes. La concurrence stimule l’innovation à un rythme effréné – chaque nouvelle génération promettant des modèles plus grands, des temps d’entraînement plus rapides et des applications plus intelligentes. Pour les praticiens de l’IA, c’est une période passionnante avec une offre matérielle plus riche que jamais. Et pour l’industrie, ce duel à trois façonnera la manière dont l’infrastructure IA sera construite et tarifée dans les années à venir, influençant en fin de compte la rapidité avec laquelle nous pourrons faire progresser les capacités de l’IA de manière durable et accessible. Pour reprendre les mots d’un analyste, « le labyrinthe du calcul IA » ne fait que devenir plus complexe et plus puissant engineering.miko.ai – et les acteurs évoqués ici sont en tête pour naviguer dans ce labyrinthe vers les prochaines avancées.

Sources :

- Page produit NVIDIA DGX B200 nvidia.com nvidia.com

- Blog technique NVIDIA MLPerf (performances Blackwell) developer.nvidia.com developer.nvidia.com

- Exxact Corp. – Spécifications Blackwell vs. Hopper exxactcorp.com exxactcorp.com

- Tom’s Hardware – Couverture AMD MI350/MI355X tomshardware.com tomshardware.com

- Communiqué de presse AMD – Feuille de route Instinct (Computex 2024) amd.com amd.com

- SMBOM News – Hausse de prix et revendications de performance AMD MI350 smbom.com smbom.com

- Google Cloud Blog – Annonce du TPU v6e “Trillium” cloud.google.com cloud.google.com

- Google Cloud Docs – Architecture et spécifications du TPU v6e cloud.google.com cloud.google.com

- ServeTheHome – Rapport sur le TPU v6e à SC24 servethehome.com servethehome.com

- NextPlatform – Analyse du TPU v6 (Trillium) nextplatform.com nextplatform.com

- Lightly.ai Blog – Benchmarks réels B200 vs H100 lightly.ai lightly.ai

- Tom’s Hardware – Lancement du MI350X (Paul Alcorn, 2025) tomshardware.com tomshardware.com

- Tom’s Hardware – Computex 2024 (Anton Shilov) tomshardware.com tomshardware.com

- Spécifications de l’AMD Instinct MI350X (tableau de Tom’s Hardware) tomshardware.com tomshardware.com

- Yahoo Finance / SeekingAlpha – infos sur les prix smbom.com (via rapport HSBC)

- Citation du vice-président d’AMD (Brad McCredie) tomshardware.com.